### UNIVERSITY OF CALIFORNIA Santa Barbara

# Athermal Laser Designs on Si and Heterogeneous $III-V/Si_3N_4$ Integration

A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

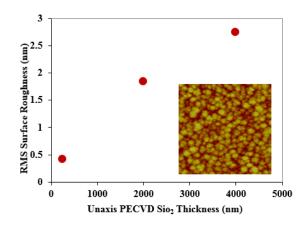

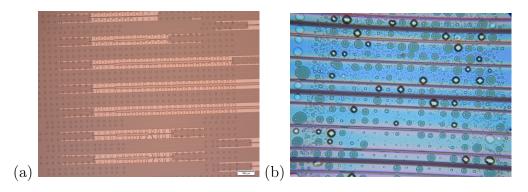

in

Electrical and Computer Engineering

by

Jock Trevor Bovington

Committee in Charge:

Professor John E. Bowers, Chair

Professor Daniel J. Blumenthal

Professor Larry A. Coldren

Dr. Richard Jones

September 2014

The Dissertation of Jock Trevor Bovington is approved:

Professor Daniel J. Blumenthal

Professor Larry A. Coldren

Dr. Richard Jones

Professor John E. Bowers, Committee Chairperson

September 2014

A thermal Laser Designs on Si and Heterogeneous  $\rm III\text{-}V/Si_3N_4$  Integration

Copyright  $\bigodot$  2014

by

Jock Trevor Bovington

I dedicate this dissertation to all the teachers of my life, most notably my family, especially my wife Ana.

### Acknowledgements

The life-long process of education is like a journey into the wilderness. You start at your home learning from those closest to you. Together you plan, discuss, and forecast. Eventually, you must leave with all of the supplies that your friends, family, and you can pull together. Supplies you all think would be helpful given the wisdom of your community's collective experience. If you're lucky, someone you meet will join you for a time, but in the end we all take our own path.

Some start with more, some with less. Most bring a map and a compass to guide their way, but the further you go the less value they have. Maps have borders and compasses mean little without a reference. In the wilderness, you must benefit from the guidance of your fellow travelers and your intuition. In the end, the attitude with which one undertakes their expedition matters more than the goods and skills they set out with.

Special thanks to my family, for providing such a wonderful home to grow up in; the town of Helena, for teaching me the meaning of community; my teachers, for challenging me; especially Prof. John Bowers, for providing a place for both my idealism and pragmatism; my committee as a whole, for all of their contributions in building the environment at UCSB and Intel where I could grow; my friends, for sharing their experiences and dreams with me; and most especially my wife, Ana, who joined me in my journey at the beginning of graduate school and has been by my side the whole time. Even when we needed to explore our own paths and meet further down the road.

As I stand on the border of the last map I have in my possession, I would like to thank my fellow travelers and the intuition I have gained from their collective wisdom. It is time to draw my own map and build new relationships on this journey into the wilderness.

### Curriculum Vitæ Jock Trevor Bovington

### Education

| 2014 | Doctor of Philosophy in Electrical and Computer Engineering, |

|------|--------------------------------------------------------------|

|      | University of California, Santa Barbara.                     |

| 2009 | Master of Science in Electrical and Computer Engineering,    |

|      | University of California, Santa Barbara.                     |

| 2006 | Bachelor of Science in Electrical and Computer Engineering,  |

|      | Seattle University.                                          |

| 2006 | Bachelor of Arts in Physics,                                 |

|      | Seattle University.                                          |

### **Professional Experience**

| 2009 | Internship, Photonic Technology Laboratory, Intel Corporation,  |

|------|-----------------------------------------------------------------|

|      | Santa Clara, California.                                        |

| 2012 | Consultant (process characterization), Praevium Research, Inc., |

|      | Santa Barbara, California.                                      |

Seattle, Washington.

#### Patent Submissions

- J. F. Bauters, J. E. Bowers, J. T. Bovington, M. R. J. Heck, M. L. Davenport and D. J. Blumenthal, "Integration of Ultra-low loss and active silicon waveguide layers."

- [2] J. T. Bovington and J. E. Bowers, "Bonding of Heterogeneous Material Grown on Silicon to Silicon Photonic Circuits."

#### **Journal Publications**

- J. T. Bovington, S. Srinivasan, and J. E. Bowers, "Athermal Laser Design," Optics express, vol. 22, no. 16, pp. 19357-19364, Aug. 2014.

- [2] J. T. Bovington, M. J. R. Heck, and J. E. Bowers, "Heterogeneous Laser Integration on Si Near Wavelengths of 1060nm," *submitted for peer review*.

- [3] J. T. Bovington, R. Wu, K. T. Cheng, J. E. Bowers, and D. J. Blumenthal, "Thermal Stress Implications in Athermal TiO<sub>2</sub> Waveguides on a Silicon Substrate," *Optics express*, vol. 21, no. 1, pp. 661-666, Jan. 2014.

- [4] M. Belt, J. T. Bovington, R. Moreira, J. F. Bauters, M. J. R. Heck, J. S. Barton, J. E. Bowers, and D. J. Blumenthal, "Sidewall gratings in ultra-low-loss Si<sub>3</sub>N<sub>4</sub> planar waveguides," *Optics express*, vol. 21, no. 1, pp. 1181-8, Jan. 2013.

- [5] J. K. Doylend, M. J. R. Heck, J. T. Bovington, J. D. Peters, M. L. Davenport, L. a Coldren, and J. E. Bowers, "Hybrid III/V silicon photonic source with integrated 1D free-space beam steering," *Optics letters*, vol. 37, no. 20, pp. 4257-9, Oct. 2012.

- [6] Y. Zheng, P. Lisherness, M. Gao, J. T. Bovington, K.-T. Cheng, H. Wang, and S. Yang, "Power-efficient calibration and reconfiguration for optical network-onchip," *Optical Communications and Networking*, vol. 4, no. 12, 2012.

- [7] H. Park, M. Sysak, H. Chen, A. W. Fang, D. Liang, L. Liao, B. R. Koch, J. T. Bovington, Y. Tang, K. Wong, M. Jacob-Mitos, R. Jones, and J. E. Bowers, "Device and Integration Technology for Silicon Photonic Transmitters," *Selected Topics in Quantum Electronics, IEEE Journal of*, vol. 17, no. 3, pp. 671-688, 2011. (invited)

- [8] J. K. Doylend, M. J. R. Heck, J. T. Bovington, J. D. Peters, L. a Coldren, and J. E. Bowers, "Two-dimensional free-space beam steering with an optical phased array on silicon-on-insulator," *Optics express*, vol. 19, no. 22, pp. 21595-604, Oct. 2011.

- [9] H. Chen, A. Fang, J. Peters, Z. Wang, J. T. Bovington, D. Liang, and J. E. Bowers, "Integrated Microwave Photonic Filter on a Hybrid Silicon Platform," *Microwave Theory and Techniques, IEEE Transactions on*, vol. 58, no. 11, pp. 3213-3219, 2010.

#### **Conference Publications**

- S. Feng, K. Shang, J. T. Bovington, R. Wu, K. Cheng, J. E. Bowers, and S. J. B. Yoo, "Athermal Characteristics of TiO<sub>2</sub>-Clad Silicon Waveguides at 1.3m," Submitted to IEEE Photonics Conference, 2014.

- C. Krckel, V. Torres-Company, P. Andrekson, J. T. Bovington, J. Bauters, M. Heck, and J. E. Bowers, "Wavelength Conversion in Low Loss Si<sub>3</sub>N<sub>4</sub> Waveguides," *CLEO: Science and Innovation, no. Nonlinear Nanophotonics* (SW3M), pp. 4-5, 2014.

- [3] J. C. Hulme, J. K. Doylend, M. J. R. Heck, J. D. Peters, M. L. Davenport, J. T. Bovington, L. a. Coldren, and J. E. Bowers, "Fully integrated hybrid silicon free-space beam steering source with 32-channel phased array," *Proc. SPIE 8989, Smart Photonic Optoelectronic Integrated Circuits XVI*, vol. 8989, p. 898907, Mar. 2014. (invited)

- [4] J. E. Bowers, J. T. Bovington, A. Y. Liu, and A. C. Gossard, "A Path to 300 mm Hybrid Silicon Photonic Integrated Circuits," *Optical Fiber Communications Conference*, p. Th1C.1, 2014.(invited)

- [5] D. T. Spencer, M. J. R. Heck, R. Moreira, J. T. Bovington, J. E. Bowers, A. Leinse, H. H. Van den Vlekkert, R. G. Heideman, M. Hoekman, and T. T. Veenstra, "Integrated single and multi-layer Si<sub>3</sub>N<sub>4</sub> platform for ultra-low loss propagation

and small bending radii," *Optical Fiber Communications Conference*, p. Th1A.2, 2014.

- [6] J. T. Bovington, R. Wu, K.T. Cheng, J.E. Bowers, "Role of thermal stress in athermal waveguide design using TiO<sub>2</sub> waveguides on a silicon substrate," *IEEE Photonics Conference*, 2013 IEEE, vol., no., pp.219,220, 8-12 Sept. 2013

- [7] H. Chen, A. Fang, J. T. Bovington, J. D. Peters, and J. E. Bowers, "Hybrid Silicon Tunable Filter Based on a Mach-Zehnder Interferometer and Ring Resonator," *International Topical Meeting on Microwave Photonics 2009*, no. 1, pp. 1-4. MWP Best Student Paper Award

- [8] A. Alduino, J. T. Bovington, et al., "Demonstration of a high speed 4-channel integrated silicon photonics WDM link with hybrid silicon lasers," *Integrated Photonics Research, Silicon and Nanophotonics. Optical Society of America*, pp. 4-6, 2010.

- [9] J. K. Doylend, M. J. R. Heck, J. T. Bovington, J. D. Peters, and J. E. Bowers, "Free-space beam steering using silicon waveguide surface gratings," *IEEE Photonic Society 24th Annual Meeting*, 2011, vol. 6, pp. 547-548.

- B. Koch, A. Alduino, L. Liao, R. Jones, M. Morse, B. Kim, W. Lo, H. Liu, H. Rong, M. Sysak, C. Krause, R. Saba, D. Lazar, R. Bar, S. Litski, A. Liu, K. Sullivan, O. Dosunmu, N. Na, T. Yin, I. Hsieh, J. Heck, R. Beatty, J. T. Bovington, and M. Paniccia, "A 4x12. 5 Gbps CWDM Si Photonics Link using Integrated Hybrid Silicon Lasers," *CLEO: Science and Innovation*, 2011, pp. 4-5.

- [11] J. K. Doylend, M. J. R. Heck, J. T. Bovington, J. D. Peters, M. L. Davenport, and J. E. Bowers, "Hybrid III-V silicon photonic steerable laser," *IEEE Photonics Conference*, 2012, pp. 1-2.

- [12] J. Doylend, M. R. Heck, J. T. Bovington, J. Peters, L. Coldren, and J. Bowers,

"Free-space Beam Steering in Two Dimensions Using a Silicon Optical Phased

Array," Optical Fiber Communication Conference, 2012, p. OM2J.1.

- Y. Zheng, P. Lisherness, M. Gao, J. T. Bovington, S. Yang, and K.-T. Cheng, "Power-Efficient Calibration and Reconfiguration for On-Chip Optical Communication," *Design, Automation and Test in Europe Conference & Exhibition*, 2012, pp. 1501-1506.

- [14] J. K. Doylend, M. J. R. Heck, J. T. Bovington, J. D. Peters, M. L. Davenport,

L. a. Coldren, and J. E. Bowers, "Hybrid silicon free-space source with integrated beam steering," *Silicon Photonics VIII*, 2013, vol. 8629, no. 1, pp. 862911-1-9.

### Abstract

## Athermal Laser Designs on Si and Heterogeneous $III-V/Si_3N_4$ Integration

Jock Trevor Bovington

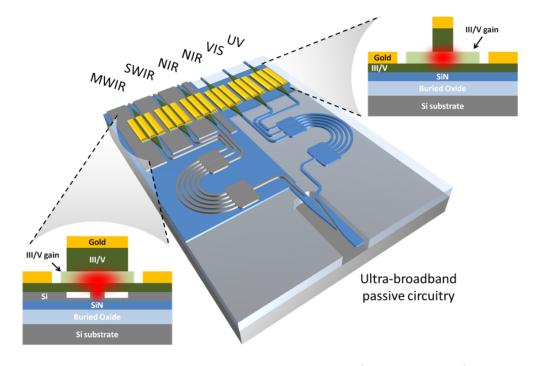

This dissertation presents each component of and a path towards heterogeneously integrated GaAs type III-V lasers bonded to  $Si_3N_4$  passive waveguides on silicon, targeting visible integrated photonics on silicon. A continuous-wave Fabry-Pérot laser, tapered mode converters from III-V to  $Si_3N_4$ , and  $Si_3N_4$  sidewall distributed Bragg reflector elements, all made with an integrable process flow, are demonstrated to prove this principle. The goal of this integration is to combine electrically pumped InGaAs multiple quantum well (MQW) active material with low-loss, spectrally wide-bandwidth waveguides to enable compact, novel photonic integrated circuits.

An additional benefit with  $Si_3N_4$  is its lower thermal drift relative to silicon. Additionally, demonstrations of TiO<sub>2</sub> based guides with ~ pm/K thermal drift are presented to explore the possibilities of athermalized waveguides on silicon. Both TiO<sub>2</sub> core and clad waveguides are studied, and new materials information on amorphous sputtered TiO<sub>2</sub> are reported. As integration with such waveguides could open opportunities for novel athermal lasers, some passively athermal designs and designs with integrated athermal wavelength references are presented which show the merit of an integrated approach.

As much process development was required to bring all of the device demonstrations presented in this dissertation to fruition, key process developments are highlighted and explained in detail to assist in any similar future developments.

Finally, the vision of heterogeneous integration as an enabler for ultra-broadband photonic integrated circuits beyond existing InP/Si photonic integrated circuits is presented as future work.

> Professor John E. Bowers Dissertation Committee Chair

### Contents

| A            | cknov                | wledge | ements                                                                             |   |   | v         |

|--------------|----------------------|--------|------------------------------------------------------------------------------------|---|---|-----------|

| $\mathbf{C}$ | urric                | ulum ` | Vitæ                                                                               |   |   | vii       |

| A            | bstra                | ct     |                                                                                    |   |   | xiii      |

| Li           | ist of               | Figur  | es                                                                                 |   | 2 | xviii     |

| Li           | ist of               | Table  | S                                                                                  |   |   | xx        |

| 1            | Intr                 | oducti | ion                                                                                |   |   | 1         |

|              | 1.1                  | Backg  | round                                                                              |   |   | 4         |

|              |                      | 1.1.1  |                                                                                    |   |   | 5         |

|              | 1.2                  | Litera | ture review                                                                        |   |   | 8         |

|              |                      | 1.2.1  | Athermal devices and designs                                                       |   |   | 8         |

|              |                      | 1.2.2  | GaAs-based devices on Si                                                           |   |   | 15        |

|              |                      | 1.2.3  | $TiO_2$ devices on Si                                                              |   |   | 17        |

|              | 1.3                  | Disser | tation overview                                                                    |   | • | 18        |

| <b>2</b>     | $\operatorname{Ath}$ | ermal  | Devices and Designs on Silicon                                                     |   |   | <b>20</b> |

|              | 2.1                  | Applie | cations and background for integrated athermal devices                             | , |   | 22        |

|              |                      | 2.1.1  | Application examples                                                               |   |   | 23        |

|              |                      | 2.1.2  | Circuit-based athermalization                                                      |   |   | 26        |

|              |                      | 2.1.3  | Waveguide and grating athermalization                                              |   |   | 27        |

|              | 2.2                  | Ather  | malized $TiO_2$ core waveguides $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | , |   | 32        |

|              |                      | 2.2.1  | Background                                                                         |   |   | 32        |

|              |                      | 2.2.2  | Waveguide geometry and fabrication                                                 |   |   | 33        |

|              |                      | 2.2.3  | Measurement setup and results                                                      |   |   | 35        |

|          |      | 2.2.4 Theory and simulations                                                                                                                                                                | 37  |

|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|          |      | 2.2.5 Conclusions of athermalized $TiO_2$ core waveguides                                                                                                                                   | 44  |

|          | 2.3  | $TiO_2$ top clad athermal rings and gratings $\ldots$                                                                                                                                       | 45  |

|          |      | 2.3.1 $TiO_2$ top clad athermal gratings                                                                                                                                                    | 46  |

|          |      | 2.3.2 $\operatorname{TiO}_2$ top clad athermal rings $\ldots \ldots \ldots$ | 48  |

|          |      | 2.3.3 Discussion on second order effects                                                                                                                                                    | 49  |

|          |      | 2.3.4 TiO <sub>2</sub> clad Si rings and gratings conclusions $\ldots$ $\ldots$ $\ldots$                                                                                                    | 52  |

|          | 2.4  | Athermal laser design                                                                                                                                                                       | 52  |

|          |      | 2.4.1 Thermal dependences of lasers                                                                                                                                                         | 53  |

|          |      | 2.4.2 Examples of integrated athermal lasers                                                                                                                                                | 55  |

|          |      | 2.4.3 Athermal laser design summary and conclusions                                                                                                                                         | 63  |

|          | 2.5  | Conclusions                                                                                                                                                                                 | 64  |

| 3        | III- | $V/Si_3N_4$ Heterogeneous Laser Integration                                                                                                                                                 | 66  |

| -        | 3.1  | Introduction                                                                                                                                                                                | 66  |

|          | 3.2  | InGaAs/GaAsP multiple quantum well lasers on Si                                                                                                                                             | 68  |

|          |      | 3.2.1 Fabry-Pérot lasers                                                                                                                                                                    | 68  |

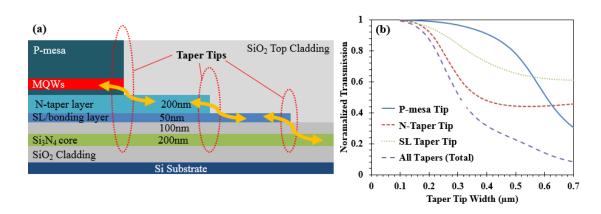

|          | 3.3  | III-V to $Si_3N_4$ tapers                                                                                                                                                                   | 78  |

|          | 3.4  | Integrated DBR mirrors in $Si_3N_4$ waveguides                                                                                                                                              | 81  |

|          |      | 3.4.1 Summary of integrated DBR mirrors in $Si_3N_4$                                                                                                                                        | 88  |

|          | 3.5  | Limiting self-heating in heterogeneous lasers with thick $SiO_2$ lower                                                                                                                      |     |

|          | clad | ding                                                                                                                                                                                        | 89  |

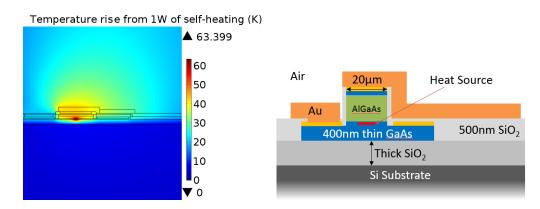

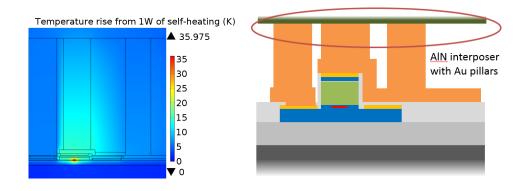

|          |      | 3.5.1 Thermal impedance modeling in COMSOL                                                                                                                                                  | 90  |

|          |      | 3.5.2 Thermal impedance of heterogeneous lasers with thick $SiO_2$                                                                                                                          |     |

|          |      | lower cladding                                                                                                                                                                              | 92  |

|          |      | 3.5.3 Thermal shunts                                                                                                                                                                        | 93  |

|          |      | 3.5.4 Flip-chip bonding                                                                                                                                                                     | 96  |

|          |      | 3.5.5 Summary of thermal design                                                                                                                                                             | 98  |

|          | 3.6  | Conclusions of III-V/Si <sub>3</sub> N <sub>4</sub> laser integration $\ldots \ldots \ldots \ldots \ldots$                                                                                  | 99  |

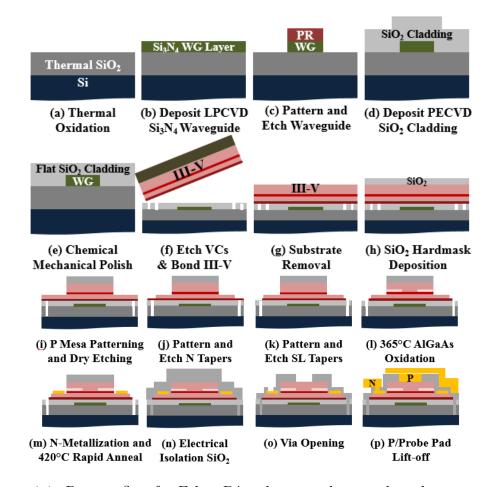

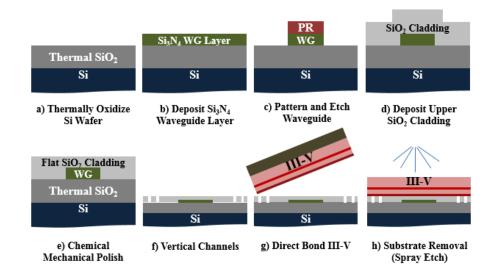

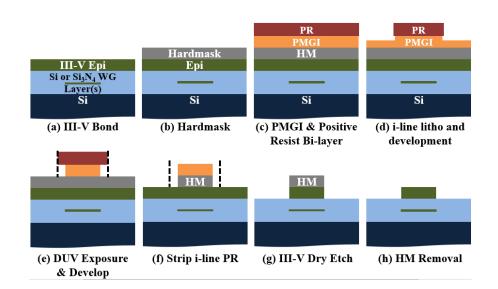

| <b>4</b> | Fab  | rication of Heterogeneous $GaAs/Si_3N_4$ Lasers                                                                                                                                             | 101 |

|          | 4.1  | Heterogeneous laser process                                                                                                                                                                 | 101 |

|          | 4.2  | Bonding                                                                                                                                                                                     | 104 |

|          |      | 4.2.1 Background and context                                                                                                                                                                | 104 |

|          |      | 4.2.2 Design decisions                                                                                                                                                                      | 107 |

|          |      | 4.2.3 Bonding results and conclusions                                                                                                                                                       | 116 |

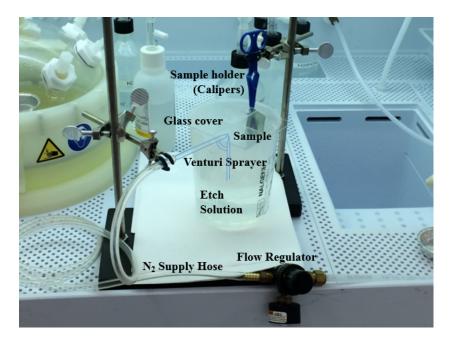

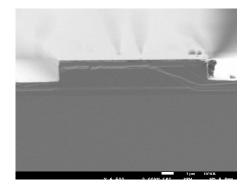

|          | 4.3  | AlGaAs mesa etch development                                                                                                                                                                | 117 |

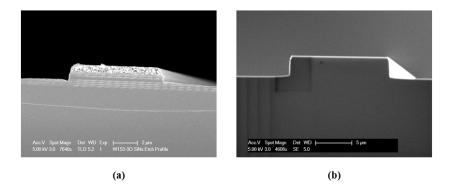

|          |      | 4.3.1 AlGaAs ICP etching in the Unaxis VLR system                                                                                                                                           | 117 |

|          |      | 4.3.2 AlGaAs ICP etching in the Panasonic ICP system                                                                                                                                        | 119 |

|          |      | 4.3.3 AlGaAs mesa etching results and conclusion                                                                                                                                            | 120 |

### xvi

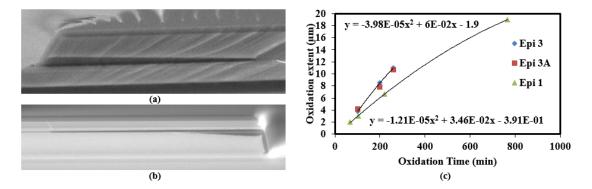

| 4.4<br>4.5   | 4.4.1Oxidation results of bonded AlGaAs4.4.2Selective area AlGaAs oxidation4.4.3Conclusion of oxidation of bonded AlGaAs epiTaper tip reduction4.5.1I-line bi-layer process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 121<br>121<br>124<br>130<br>131<br>132<br>136 |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 5 Sur        | nmary and Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 190                                           |

| o bui        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 138                                           |

| 5 5ui<br>5.1 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1 <b>38</b><br>138                            |

| ·            | Summary and conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                               |

| ·            | Summary and conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 138                                           |

| ·            | Summary and conclusions $\ldots$ </th <th>138<br/>139</th> | 138<br>139                                    |

| ·            | Summary and conclusions $\ldots$ $\ldots$ $\ldots$ $\ldots$ 5.1.1Athermal devices and designs on Si $\ldots$ $\ldots$ 5.1.2III-V/Si <sub>3</sub> N <sub>4</sub> heterogeneous laser integration $\ldots$ $\ldots$ 5.1.3Fabrication of heterogeneous GaAs/Si <sub>3</sub> N <sub>4</sub> lasers $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 138<br>139<br>140                             |

### List of Figures

| 1.1  | Schematic of III-V / $Si_3N_4$ or $TiO_2$                                                                                                                                                                    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2  | Athermal packaging of a conventional AWG                                                                                                                                                                     |

| 1.3  | Use of a bimetal substrate mount for thermal compensation 9                                                                                                                                                  |

| 1.4  | Spectra from athermally packaged fiber Bragg grating 10                                                                                                                                                      |

| 1.5  | Athermal packaging for fiber Bragg grating                                                                                                                                                                   |

| 2.1  | Improving spectral efficiency                                                                                                                                                                                |

| 2.2  | Athermal circuits examples                                                                                                                                                                                   |

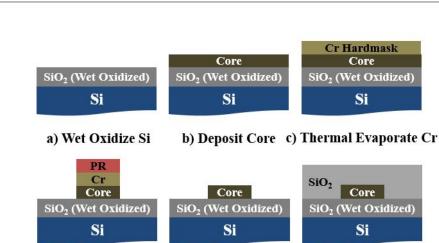

| 2.3  | $TiO_2$ core waveguide process flow summary                                                                                                                                                                  |

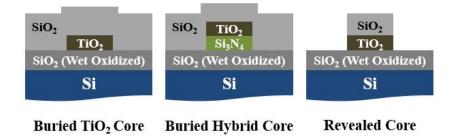

| 2.4  | Types of $TiO_2$ core waveguides $\ldots \ldots \ldots \ldots \ldots \ldots \ldots 35$                                                                                                                       |

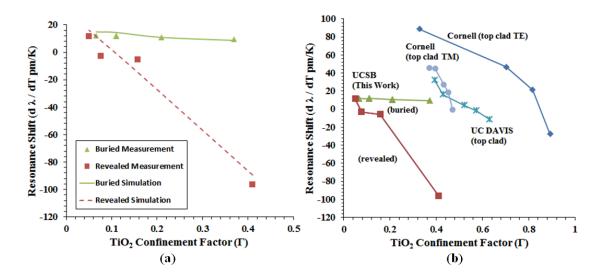

| 2.5  | Athermal measurement results                                                                                                                                                                                 |

| 2.6  | Athermal model comparison                                                                                                                                                                                    |

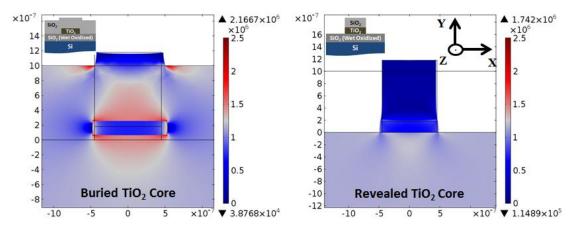

| 2.7  | FEM thermo-stress-optical simulations                                                                                                                                                                        |

| 2.8  | $TiO_2$ clad Si gratings                                                                                                                                                                                     |

| 2.9  | $TiO_2$ clad Si grating Bragg wavelength v. temperature $\ldots \ldots 47$                                                                                                                                   |

| 2.10 | $TiO_2$ clad Si ring cross section                                                                                                                                                                           |

|      | $TiO_2$ clad Si ring measurements $\ldots \ldots \ldots$                                     |

|      | Typical laser thermal drift                                                                                                                                                                                  |

|      | Athermal laser examples                                                                                                                                                                                      |

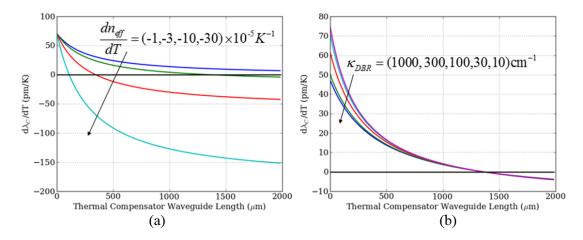

|      | Athermal DBR compensator length simulation                                                                                                                                                                   |

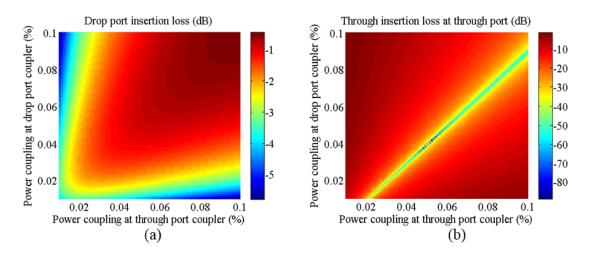

|      | Intracavity ring insertion loss                                                                                                                                                                              |

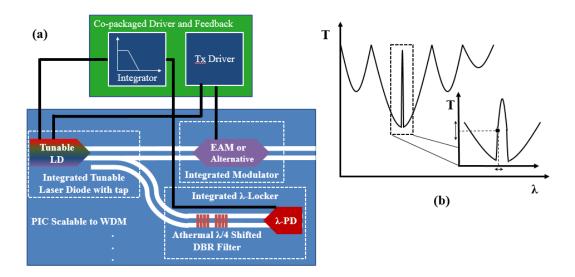

| 2.16 | Integrated wavelength locker                                                                                                                                                                                 |

| 3.1  | Schematic of III-V/Si <sub>3</sub> N <sub>4</sub> heterogeneous laser $\ldots \ldots \ldots$ |

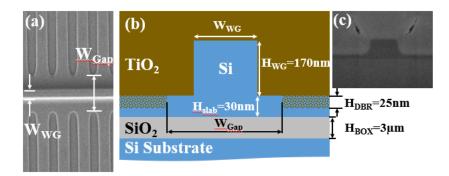

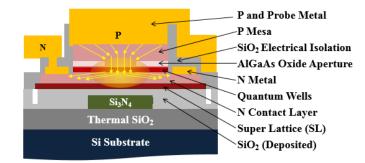

| 3.2  | Fabry-Pérot laser cross-section                                                                                                                                                                              |

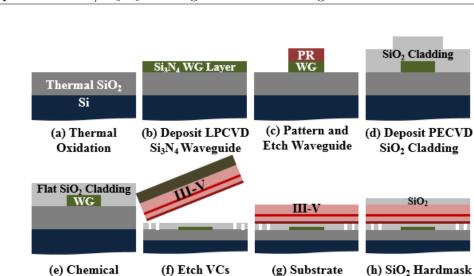

| 3.3  | Fabry-Pérot laser process flow                                                                                                                                                                               |

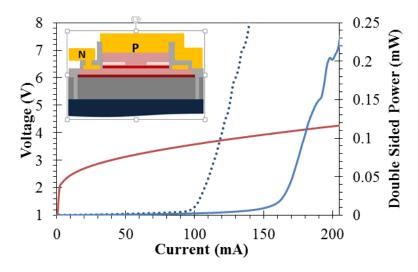

| 3.4  | Continuous-wave LIV                                                                                                                                                                                          |

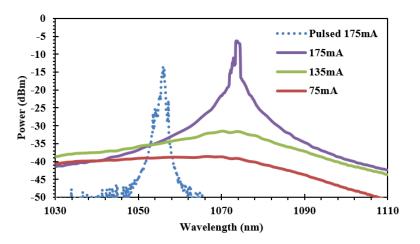

| 3.5  | Fabry-Pérot spectra                                                                                                                                                                                          |

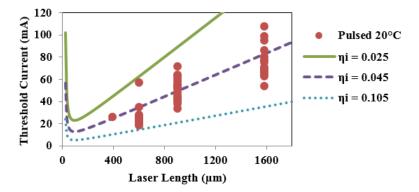

| 3.6  | Pulsed cutbacks                                            | 75  |

|------|------------------------------------------------------------|-----|

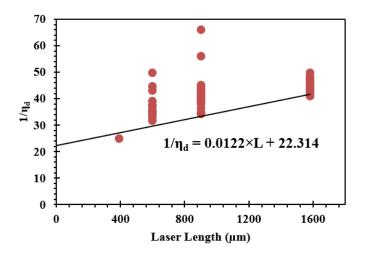

| 3.7  | Pulsed cutbacks v. inverse differential quantum efficiency | 76  |

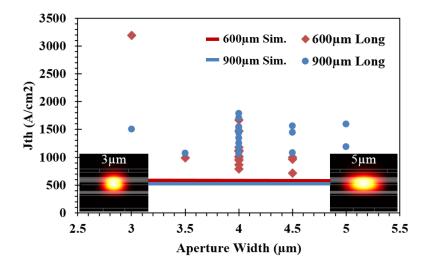

| 3.8  | Pulsed thresholds v. aperture width                        | 77  |

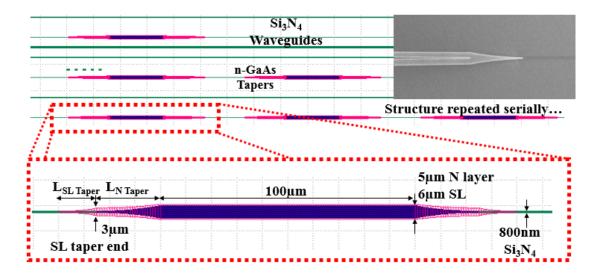

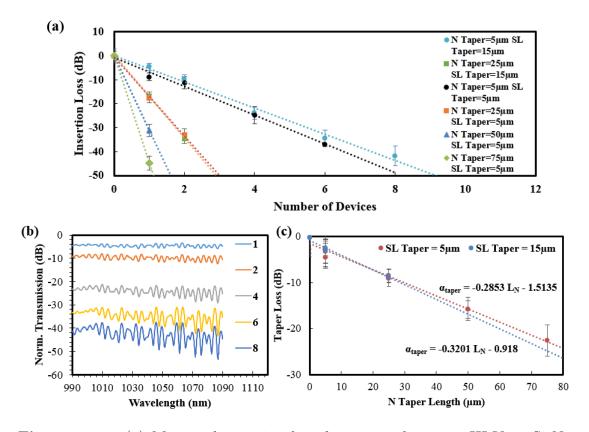

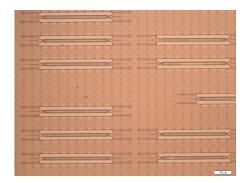

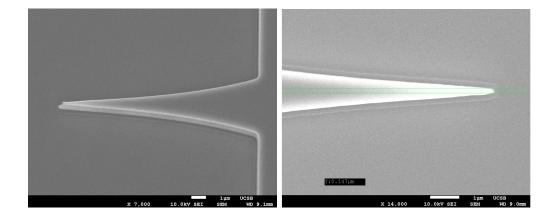

| 3.9  | Taper repeat structures                                    | 79  |

| 3.10 | Taper loss results                                         | 80  |

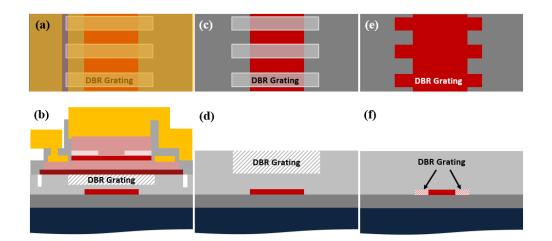

| 3.11 |                                                            | 83  |

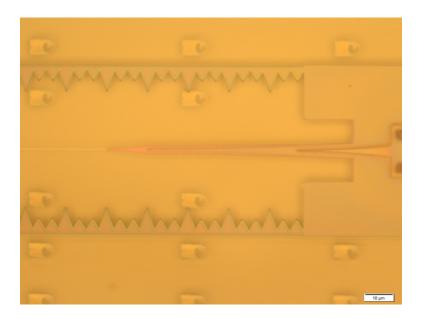

| 3.12 | Side-wall DBR in $Si_3N_4$ buried channel waveguide        | 85  |

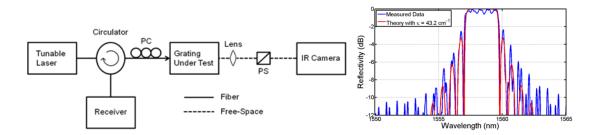

|      | DBR measurement setup and characteristic spectra           | 86  |

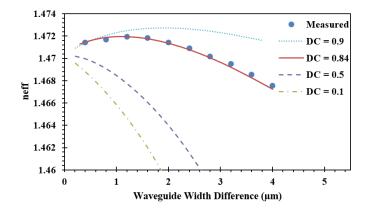

|      | $n_{eff}$ of sidewall DBRs                                 | 88  |

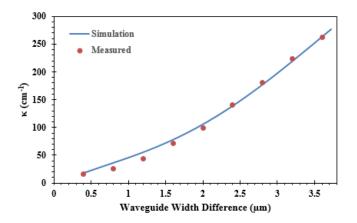

|      | Grating strength of sidewall DBRs                          | 89  |

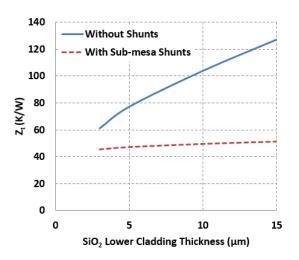

|      | Unshunted lasers with thick $SiO_2$ lower cladding         | 92  |

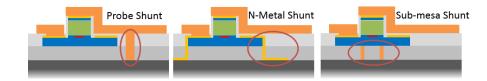

|      | Thermal shunt types                                        | 93  |

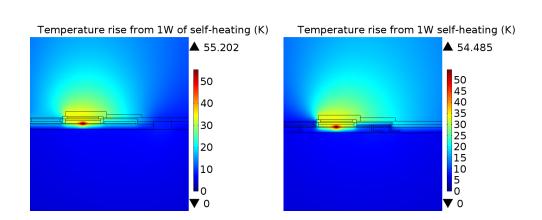

|      | Comparison of probe and n-metal shunts                     | 94  |

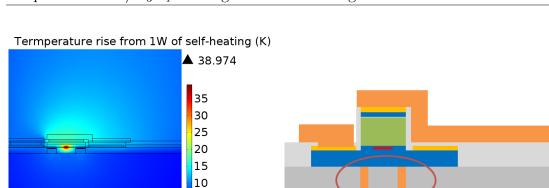

|      | Sub-mesa shunts                                            | 95  |

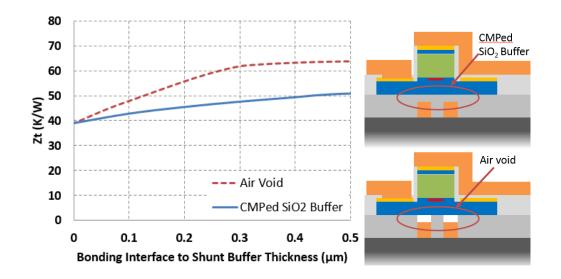

|      | Comparison of sub-mesa shunt buffers                       | 96  |

|      | Thermal impedance vs. $SiO_2$ lower cladding thickness     | 97  |

|      | Improvement of thermal impedance by flip-chip bonding      | 98  |

|      |                                                            |     |

| 4.1  |                                                            | 102 |

| 4.2  | 1 / 1                                                      | 108 |

| 4.3  | 0 1                                                        | 109 |

| 4.4  | 20                                                         | 111 |

| 4.5  | 01                                                         | 113 |

| 4.6  |                                                            | 115 |

| 4.7  |                                                            | 116 |

| 4.8  | 1                                                          | 118 |

| 4.9  | 1                                                          | 119 |

| 4.10 | AlGaAs oxidation rates and cross sections                  | 122 |

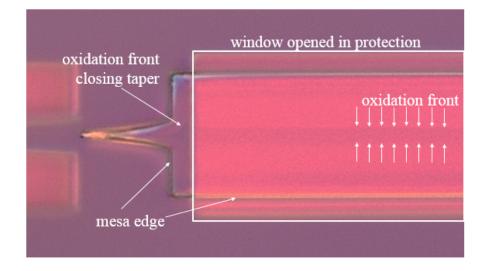

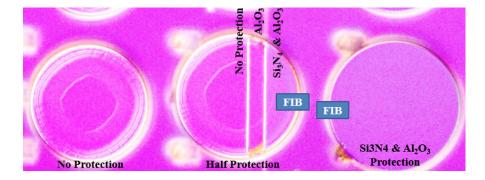

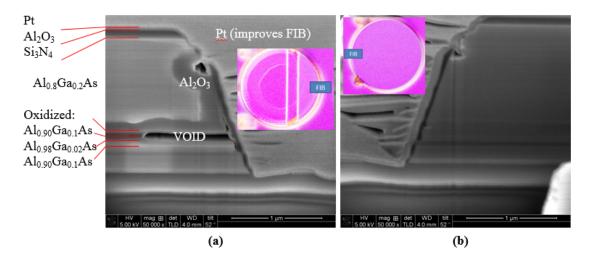

|      | 1 1                                                        | 125 |

|      | 1                                                          | 126 |

|      | 1 / 1                                                      | 128 |

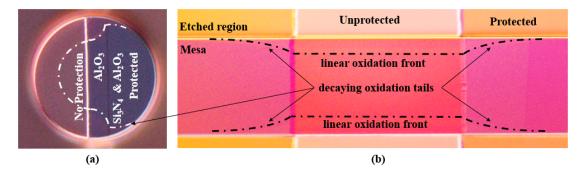

| 4.14 | Accelerated oxidation on protected edges                   | 129 |

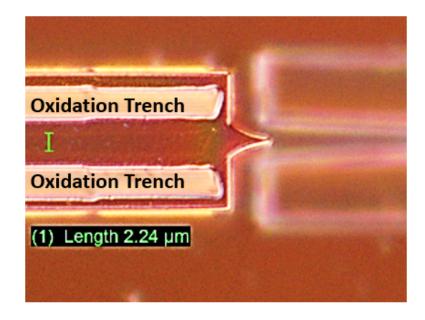

| 4.15 | Oxidation trenches                                         | 130 |

| 4.16 | Taper tip reduction argument                               | 131 |

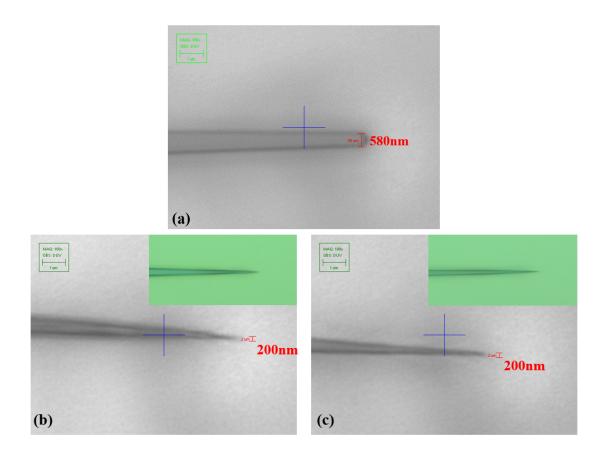

| 4.17 | Bi-layer taper tip reduction process                       | 133 |

| 4.18 | Bi-layer taper tip reduction images                        | 134 |

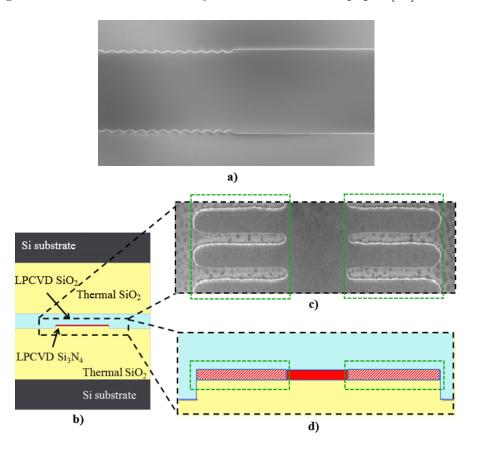

|      |                                                            | 136 |

| 4.20 | Fabricated 3 layer taper                                   | 137 |

| 5.1  | Ultra-broadband source                                     | 143 |

### List of Tables

| 1.1                 | Approximate substrate minimum cost and maximum size $[1]$                                                                                                                                                                                                            | 6                                        |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| 2.1<br>2.2<br>2.3   | Material properties used in CMOS compatible athermal waveguides<br>Comparison of thermo-optic models and measured data<br>Material properties for simulation ( $\lambda_0$ =1550 nm)                                                                                 | 32<br>40<br>41                           |

| $3.1 \\ 3.2 \\ 3.3$ | Epitaxial layer design for Fabry-Pérot lasers $\ldots \ldots \ldots \ldots \ldots$<br>Epitaxial layer designs for III-V to Si <sub>3</sub> N <sub>4</sub> taper structures $\ldots \ldots$<br>Material properties used in COMSOL thermal simulations $\ldots \ldots$ | 72<br>78<br>91                           |

| $4.1 \\ 4.2$        | Coefficients of thermal expansion (CTE) of substrate materials<br>Epitaxial layer designs for oxidation apertures                                                                                                                                                    | $\begin{array}{c} 105\\ 123 \end{array}$ |

## Chapter 1 Introduction

This thesis is focused on the heterogeneous integration of the best individual and combinations of photonic materials onto a single platform on silicon. This is a vision shared by many at UCSB, particularly in John Bowers' optoelectronics group, and elsewhere around the world, as evidenced by the large number of publications and conference presentations on the topic in recent years. More recently the funding and focus has shifted toward longer wavelengths in the research community for MIR applications related to molecular sensing and military applications thanks to the intrinsic properties of Si and Ge at these longer wavelengths [2, 3]. Unique to this work is a focus on wavelengths shorter than the bandgap of silicon. For this reason, the standard silicon waveguide designs no longer work below 1.1  $\mu m$  and a wider bandgap material such as silicon-nitride (Si<sub>3</sub>N<sub>4</sub>) or titanium-dioxide (TiO<sub>2</sub>) must be used for passive circuitry. For active III-V materials, GaAs based semiconductors are used to demonstrate lasers as they are the key and in many ways most challenging of devices to integrate.

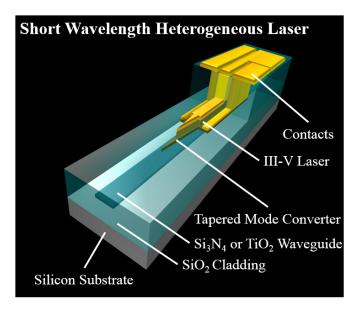

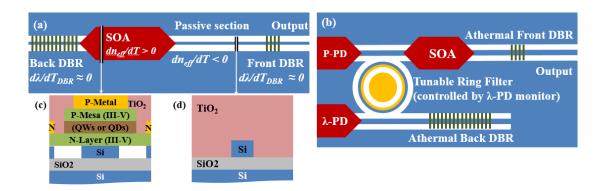

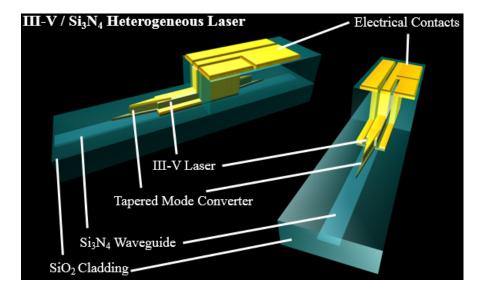

Beyond the discussion of shorter wavelength lasers on silicon, reductions in thermal sensitivity, or athermalization are covered. Applications at all wavelengths are sensitive to temperature, so all of the arguments and measurements presented for telecommunications also apply at short wavelengths and for sensing applications. So, a broader study was made of the reduced thermal sensitivity of  $TiO_2$  waveguides. As III-V devices are not naturally paired with  $Si_3N_4$  or  $TiO_2$ waveguides, the method of integrating the two together requires integration. For this, we propose heterogeneous integration by wafer bonding. A schematic of this structure is shown in Fig. 1.1.

This dissertation specifically is an exploration into new possibilities of heterogeneous integration on silicon. Subjects explored include a path towards integration of GaAs type III-V lasers with  $Si_3N_4$  planar lightwave circuits (PLCs), and the use of TIO<sub>2</sub>, an athermalizing core or cladding material, for the purposes of athermal passive circuitry. As athermal waveguide circuits are of particular interest for passively athermalized circuits for optical communications, some tests were conducted at telecommunication bandwidths. Both of these waveguides are capable of higher energy densities and lower losses than silicon and are transparent to wavelengths below the silicon band gap, which is unique to this work. Prior

Figure 1.1: Schematic of heterogeneous integration of III-V laser with broadband  $Si_3N_4$  or  $TiO_2$  waveguide. (artwork courtesy of Martijn Heck)

art in heterogeneous integration of III-V and Si has focused on O and C-band [4] and some recent longer wavelength demonstrations [5].

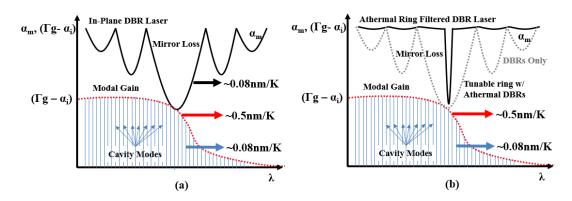

Finally, in exploring both of the topics of III-V on silicon integration and athermalization together, some athermal laser designs are proposed theoretically with the intention of reducing the amount of feedback required in a conventional laser thermal stabilization approach. Unique to this approach, the stabilized wavelength references are integrated rather than relying on an external wavelength locker.

### 1.1 Background

This work was completed in the context of previous successful heterogeneous integrations which the reader should be aware of. In 2005, Hyundai Park, Alexander Fang and colleagues produced the world's first Hybrid Silicon Laser [6]. This was a heterogeneous integration of III-V InP based gain material on to partially processed silicon photonic circuits using die-scale 300°C O<sub>2</sub> plasma assisted molecular wafer bonding. The term hybrid in this case is different from, but may easily be mistaken with, prior work of photonic "hybridization." Prior hybridization of pre-processed lasers with photonics circuits was commercialized by companies like CIP Technologies (acquired by Hauwei in January 2012) and later by silicon photonics companies like Kotura (acquired by Mellanox in August 2013) and Oracle. These approaches use pre-fabricated III-V devices typically metal-bonded to host circuits similarly to flip-chip bonding. There is an understandable confusion that remains to this day as Intel Corporation, the most visible supporter and developer of III-V/Si technology, has taken on the Hybrid Silicon Laser name into it's marketing that at the time of this writing has gained a great deal of attention within the community. To avoid confusion, this dissertation adopts the nomenclature "heterogeneous" III-V/Si integration used by Aurrion, the company formed by Alexander Fang and Prof. John Bowers to move the technology out of the lab

and into the market. This refers to all technologies that bond III-V mid-process and then use wafer-scale lithographic processes to complete the III-V fabrication.

Heterogeneous, meaning simply "consisting of dissimilar or diverse ingredients or constituents" [7], is an appropriate term for the content of this work as the scope of this work covers a range of concepts and technologies which are made possible by the pairing of two or more different materials, platforms, or concepts.

Further context of this work is the broader and more longstanding emergence of Silicon Photonics, or more accurately the emergence of photonics on silicon whose distinction is made in Section 1.1.1. Briefly, the promise of photonics technology leveraging the investments in time, equipment, facilities, and human knowledge of the CMOS fabrication industrial revolution to make lower cost and higher quality components at previously unseen scales. Scale in terms of both higher volumes and in many cases smaller and simpler devices and packages.

It is through this lens that I have focused my efforts.

### 1.1.1 The value of photonics on silicon, not just in silicon

The tremendous amount of focus given to Silicon Photonics in the past decade as the platform promising to drive down costs and improve reliability while frequently providing more dense and complex integration. Technical conference presentation rooms have flooded out the doors with eager participants in this technological shift. The argument I wish to make here, simply stated, is that most of these advantages are not about Si device layers at all, but rather about the use of Si substrate in "CMOS" fabrication facilities with their years of development in equipment and personnel and substantial investment in the facilities themselves. I emphasize that these photonics processes need not necessarily be CMOS processes to leverage the advantages of CMOS.

The photonic technologies presented in this dissertation are not in Si at all, with the exception of  $TiO_2$  clad Si results presented in 2.3, but rather on Si so as to achieve compatibility with Si fabrication facilities. I argue that this approach earns most merits of Silicon Photonics and potentially gains additional advantages by not using Si optical properties. Hence, I will refer to these technologies more broadly as Photonics on Silicon, focusing particularly on III-V Photonics on Silicon.

With regard to the oft-quoted merit of silicon photonics, cost reduction, Table 1.1 provides some economic perspective on the use of silicon-on-insulator (SOI) substrates, the backbone of Silicon Photonics.

Table 1.1: Approximate substrate minimum cost and maximum size [1]

|                                    | InAs  | InP  | GaAs | SOI  | Si   |

|------------------------------------|-------|------|------|------|------|

| Minimum Substrate Cost ( $/cm^2$ ) | 18.25 | 4.55 | 1.65 | 1.30 | 0.12 |

| Maximum size (mm)                  | 75    | 150  | 200  | 450  | 450  |

As is clear from Table 1.1, using SOI is an order of magnitude more expensive than directly using Si substrates, comparable in cost to a GaAs substrate, and a few times cheaper than InP, though InP and GaAs are not available at the larger sizes of Si and SOI. Therefore, passive elements in SOI, though compact, do not have an inherent cost advantage over conventional planar lightwave circuit (PLC) technology on Si.

Non-silicon waveguides using  $Si_3N_4$  or  $TiO_2$  have broader spectral bandwidth, lower thermal drift, and in many cases lower loss than Si waveguides. These waveguides can be implemented without SOI and therefore can be both lower cost and higher performance.

With regards to active component integration, again the cost of SOI is limiting in some cases. Simple heaters are available in PLCs for phase tuning and advanced circuits requiring lasers and high-speed modulation and detection need not be available in large areas of the PIC's passive elements, such as arrayed waveguide gratings (AWGs). The most-economic design would not be a completely monolithic III-V, nor would it be heterogeneous or hybrid integration of III-V on SOI, it would likely come from a heterogeneous or hybrid integration on bulk silicon that keeps passive elements in well established PLC technology on Si. This type of integration is where the line is drawn between Silicon Photonics and Photonics on Silicon.

### 1.2 Literature review

This section presents an overview of the prior art in the fields discussed in later chapters. Each subsection corresponds to the different Chapters 2, 3, and 4.

### 1.2.1 Athermal devices and designs

Managing temperature fluctuations in optical devices is not a new problem, it as old as the field itself and I could fill 100 pages with references on the topic. However, more recently the desire to develop uncooled circuits for silicon photonic devices has reinvigorated efforts to develop new solutions. I therefore focus mostly on silicon photonic efforts with an exception to circuit based schemes as those ideas would apply to many platforms. I will also refer to select non-silicon works as a potential inspiration for the solutions currently pursued on Si.

Packaging based athermal solutions: PLCs on Silicon offer superior passive components for most applications due to the highly reproducible fabrication and the tolerances of working with silica and silicon nitride compared to higher index difference waveguides. Additionally, fiber based gratings are implemented in a number of systems because of the maturity of that technology. Both in-plane and fiber-based solutions are typically dominated by material thermo-optical (TO) behavior in SiO<sub>2</sub>. However, there is also a component of their drift with can be

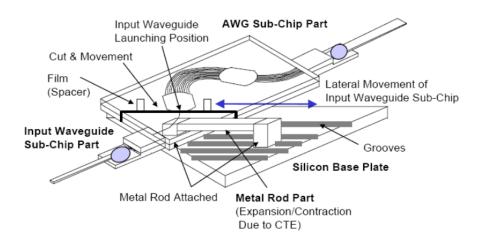

Figure 1.2: Schematic of athermal packaging solution for a conventional AWG. [8].

owed to thermal expansion of the actual optical path length. This is material specific and dominated by  $SiO_2$  cladding in the case of fiber and Si in the case of in-plane devices fabricated on Si. To overcome both the material TO effects

Figure 1.3: Schematic configuration of AWG multiplexer with bimetal plate and the corresponding change in temperature dependent spectral response. [9].

and thermal expansion, products and demonstrations have been made to force the optical path length to remain fixed or even shrink by means of an external packaging solution shown in Fig. 1.2. In another example, a bimetal "stresser" attached to a conventional device can counteract the waveguide and substrate's natural inclination to both expand and bow, thereby compensating both material TO and path length effects of  $SiO_2$  waveguides with stress as shown in Fig. 1.3.

50GHz ITU Reference Thermal Stability

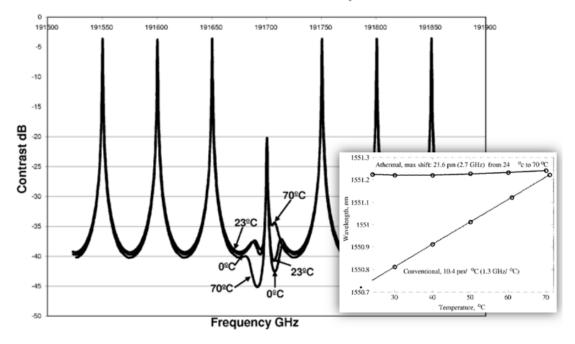

Figure 1.4: Spectral response and temperature dependent Bragg wavelength plots for athermally packaged fiber Bragg grating. [10].

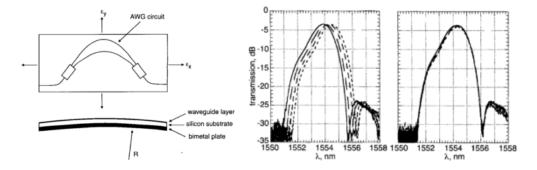

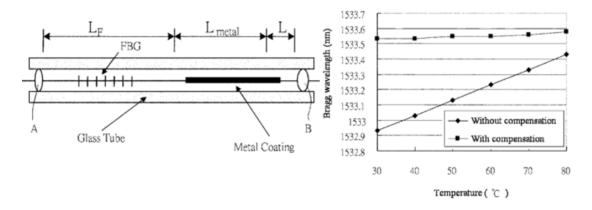

For fiber Bragg gratings (FBGs), attaching the fiber to a single similar bimetal stack is not entirely sufficient, so methods of fixing the gratings to a structure that can be compressed or expanded from the two ends of the grating based on external structures of appropriately balanced thermal expansion coefficients have been implemented and achieve <0.5pm/K up to 70°C shown on Fig. 1.4. Metal

coatings have also been added to sections of fiber adjacent to the FBG and then pinned to a mount of lower thermal expansion than the metal coating. This acts to put strain on the FBG in opposition to it's natural inclination to expand and in opposition to the TOC of the waveguide of the fiber shown in Fig. 1.5.

Figure 1.5: Schematic and temperature dependent wavelength response of an athermal packaging solution for a fiber Bragg grating [11].

In summary, there exist packaging solutions based on similar principles to counteract the thermal effects present in optical devices. However, most of these are for a single device and may not scale to a tightly packaged integrated circuit with devices placed in different orientations and locations on the die or consisting of different materials and or varied optical confinement within the same materials. In other words, one packaging solution does not fit all devices in a circuit.

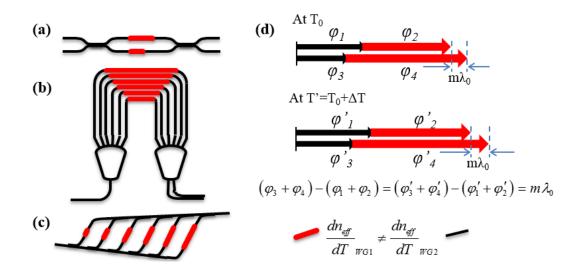

**Circuit based athermal solutions**: A number of clever circuits based athermal solutions have been implemented, most notably that of an athermal, or temperature insensitive imbalanced Mach-Zehnder interferometer (MZI) filter [12] and arrayed waveguide grating (AWG) [13]. These function by making the phase difference of the two paths temperature insensitive rather than the entire path itself as with the packaging solution. As these are interferometric devices, their transmission is based on this phase difference and therefore the transmission aptitude remains unchanged if the phase differences are locked over a wider temperature range.

This solution works for finite impulse response (FIR) filters and multiplexers but is not easily translated to infinite impulse response (IIR) rings and Bragg gratings or locking the cavity mode drift in a laser as is discussed more in depth in Sections 2.1.2 and 2.4. For this problem, there is a body of work on finding better materials to overcome thermal drift issues.

Organic materials based athermal solutions: Many polymers show very strong negative thermo-optical coefficients (TOCs) and can, therefore, be used to offset positive TOC materials like III-Vs, Si, and SiO<sub>2</sub>. Polymers have been used for top claddings for surface Bragg gratings [14], low index claddings for SiO<sub>2</sub> cores [15], as the core material itself [16], and over cladding for high index SOI waveguides with and without slots ([17], [18], [19], [20]) to enhance confinement in the polymer and in AWGs [21] [22].

However, such polymers suffer from environmental sensitivity and degradation. They often change behavior within oxygen exposure, plasma treatment, UV exposure, humidity and high temperature, and age more rapidly than other part of a product [23]. Understandably, this is not a fair generalization with all polymers for all applications, but it is a common counterpoint to consider when choosing them for your application. Finally, integration of such material into a CMOS facility can be met with resistance as they are not well established and therefore present a risk to existing processes that must be evaluated on a per facility basis.

Inorganic materials based athermal solutions: For this reason inorganic materials, such as TiO<sub>2</sub> discussed in Chapter 2, are under serious consideration for compensation of thermal drift on Si. Ta<sub>2</sub>O<sub>5</sub> is another such candidate with a negative TOC [24]. Sputtered TiO<sub>2</sub> as an overcladding for silicon waveguides was first shown by Alipour to significantly reduce thermal drift of a ring [25]. Later demonstrations by [26] & [27] near 1550 nm showed additionally promising results with implementations in Si ring based modulators and for both polarizations.

Some demonstrations were made with TiO<sub>2</sub> as a core material, but they did not focus on the thermal characteristics of these guides [24] [28]. Therefore, no comparisons could be made with the thermal measurements of TiO<sub>2</sub> core waveguides presented in Section 2.2. However, earlier demonstrations of TiO<sub>2</sub> co-deposited with SiO<sub>2</sub> did target athermal behavior and achieved <1 pm/K [29].

**Trimming**: Interestingly few of the material based athermalization reports discussed trimming the devices post-fabrication, though nearly all used a ring

structure to characterize the athermal nature of their devices. The narrow resonances in rings, in particular, are very sensitive to fabrication variation. Therefore, a method of tuning to a resonance post-fabrication or as an intermediate fabrication step is vital. This is particularly an issue on silicon as a simple and common tuning mechanize, thermal tuning, would be useless in an off-resonance athermal ring. In silicon, implantation based index tuning has been demonstrated as a potential solution to this trimming problem. Once the index change caused by the defect of the implantation is made, the trimming process can be achieved by some form of local heating to reverse the index perturbation, for example by annealing [30], or locally with a focused laser, for example [31].

Alternatively, a  $Si_3N_4$  top layer to a Si ring can be patterned and etched on a per ring basis in an automated process whereby the partially fabricated ring is tested at wafer level, and then a programmable lithographic step such as electron beam lithography is used as demonstrated in [32,33]. This is more appealing than the implantation process as the additional loss of implantation can be greater than the scattering loss due to surface roughness of the tuned  $Si_3N_4$  over cladding.

In an alternative trimming process, a UV photosensitive  $As_2S_3$  chalcogenide glass partial upper cladding has been deposited on a silicon waveguide. The effective index of the mode can then be trimmed by selective UV exposure of circuit elements. This has been further top clad with a negative TO polymer [34]. This is the ideal case, where a device can both be trimmed and made athermal. We have yet to demonstrate this, but  $As_2S_3$  chalcogenide glass could be used as the upper cladding of the athermal revealed waveguides shown in 2.2. Assuming this proves reliable, this is an excellent future direction for this work.

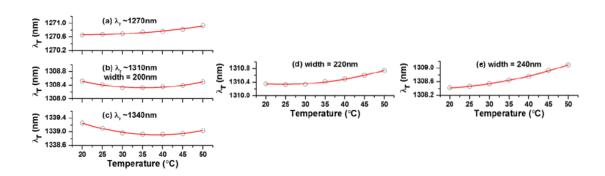

Higher order effects: One topic also often overlooked by the literature on athermalization of structures in silicon is the higher order TOC of Si itself. Across the functional temperature range of Si for most applications  $dn/dT_{Si}$  has been measured to change from  $1.85 \times 10^{-4} K^{-1}$  (at 300K) to  $>2.0 \times 10^{-4} K^{-1}$  (at 380K) [35]. This may seem like a small shift, but athermalizing materials such as polymers also have higher order changes in dn/dT with temperature and in the same direction [22] & [36]. The result can be a strong quadratic resonance drift with temperature, perhaps hidden by the small temperature ranges of many publications. We too witnessed this effect in TiO<sub>2</sub> clad silicon rings tested near 1310 nm and a summary of this finding will be presented in Section 2.3.

#### 1.2.2 GaAs-based devices on Si

Bonding of GaAs to Si: There were some early attempts to transfer InGaAs quantum well active material onto  $SiO_2$  on silicon, similar to the work presented in this dissertation, but without the intention of photonic integration with PLC waveguides. Successful transfers and characterization of these films were made as

early as 1989 and showed that a high material quality could be retained following lift-off and film transfer by use of a hydrophilic van der Waals bond [37]. Later lasers were actually fabricated using spin-on-glass as an intermediate layer [38]. Similar spin on glass bonding was conducted as part of this work at UCSB. However, voids were more numerous and the curing temperature was higher which lead to an increase in bonding related defects, so this process was abandoned in favor of plasma assisted bonding.

The problem of defect migration from the bonding interface was identified early as an issued with all such bonding processes involving substrates with dissimilar coefficients of thermal expansion. It was proposed to add an intermediate layer near the bond interface to reduce this issues as early as 1998 [39]. The details of the most appropriate intermediate layer were not clearly defined at this point, however we discuss work in bonding superlattice structures which have been shown to be highly effective in InP heterogeneous devices in Section 4.2.2.

Electrical interfaces between Si and GaAs have also been pursued, with intermediate layers from metal/solder bonding interfaces [40] and [41], to InP [38] or Sn doped SeS<sub>2</sub> [42]. However, a potentially preferable direct bonding approach has been demonstrated for highly doped p-GaAs to p-Si interfaces and even fabricated into CW quantum dot lasers [43]. Growth of GaAs on Si: Many would argue that growth of III-V material on Si is the best approach and it is therefore an active area of research. Owing to the lattice mismatch of GaAs and Si intermediate layers are also required to achieve quality device material in the grown III-V. These layers either are full of defects themselves making them not desirable optically and/or electrically, or it is made of a narrow band gap material like Ge which would rapidly absorb the light passing through it. There may indeed be a path forward for direct growth of GaAs type material on Silicon Photonics circuits, as performance in this area is continuously improving with very promising QD on Si results coming out of several groups [44], [45]. However, I would argue that the benefit of such growth may first be realized as a low-cost growth substrate for material used in a selective area die bonding approach as discussed in [1]. Again, this need not be to SOI, but could be at shorter wavelengths with a bulk Si PLC carrier with small III-V device areas.

#### 1.2.3 $TiO_2$ devices on Si

$TiO_2$  is a wide band semiconductor (>3 eV) which has previously been used for a high-k dielectric in Si transistors. Additional examples of  $TiO_2$  in resistive switching memory devices [46] and as the gate for MOS capacitors [47] show that though it has since been eclipsed by  $HfO_2$  as the gate oxide of choice, it still is a CMOS compatible material making it a negative TOC material of least resistance for introduction to a CMOS facility.

A fairly detailed process flow for a TiO<sub>2</sub> top clad silicon modulator is provided in [26] including a nice presentation of process conditions for the sputtered TiO<sub>2</sub> and the resulting figures of merit n and dn/dT. Loss data was reported for these waveguides from 1-9dB/cm increasing with decreasing waveguide width. A more direct measurement of similar material was made using a coupled prism propagation loss measurement which found a propagation loss of 0.4dB/cm verifying TiO<sub>2</sub> as a low loss material [24]. These works also made an important observation about the thermal budget of TiO<sub>2</sub>. Both attributed significant increases in loss to anatase crystal formation at temperatures as low as 350°C. This matches additional publications on the material characterization of TiO<sub>2</sub> which show first anatase, then rutile crystal transitions with increasing anneal temperatures [48].

### **1.3** Dissertation overview

The dissertation is broken into three main chapters followed by a conclusion and future work chapter. The following three chapters cover athermalization on silicon; a path towards heterogeneous integration of GaAs type lasers with  $Si_3N_4$  core waveguides on silicon, and finally a chapter on key fabrication developments on this path.

The type of athermalization which this dissertation focuses on is materialsbased waveguide athermalization explicitly with TiO<sub>2</sub>, as it is semiconductor based CMOS compatible material, with both an index ~ 2.2 or greater at 1550, and a thermo-optic coefficient about as strong as Si, but negative. The type of heterogeneous integration which Chapter 3 focuses on is of InGaAs/GaAsP multiple quantum well lasers grown on GaAs transferred to the SiO<sub>2</sub> partial upper cladding of a Si<sub>3</sub>N<sub>4</sub> strip waveguide by low-temperature O<sub>2</sub> plasma assisted bonding for laser integration. Chapter 4 has some details and rationale behind the processing used in this dissertation. Importantly, more than just a process follower both successes and failures, and the insights gained through the development are presented. The final chapter summarizes the findings of this dissertation and gives an outlook for the future.

## Chapter 2

## Athermal Devices and Designs on Silicon

Thermal stability is an important topic in integrated photonics research. The need for athermal structures is clear for photonics applications from low-cost communications links in data centers, passive optical networks, microwave photonic filters and sensors. The current solutions use either single channels, coarse wavelength division multiplexing (CWDM), temperature stabilizing feedback loops or a power hungry thermo-electric cooler (TEC).

This is an active research area with a number of solutions to address this challenge by designing intrinsically athermal structures. We would classify them into packaging solutions [8, 9, 49], circuit-based approaches [12, 13, 50], and materials solutions. Among the materials solutions, the overwhelming majority have used polymers [22]. Oft-quoted issues with these polymer-based solutions include process compatibility, performance degradation, long-term reliability, and narrowed operating temperature conditions. Much work to address these concerns continues, and in the end such solutions may be useful. However, titania (TiO<sub>2</sub>) has recently been suggested as a CMOS compatible alternative material to polymers for enabling athermal waveguides in photonic integrated circuits [51]. The reason for this is its strong negative material thermo-optic coefficient (TOC) dn/dT. Literature has quoted its TOC in a range of  $-(1-6.5) \times 10^{-4} K^{-1}$  partially due to deposition method [26, 51, 52].

This chapter holds application examples, device demonstrations, numerical simulations, and theoretical explorations of using  $TiO_2$  as a CMOS compatible athermalizing material on Si. This type of athermalization has not been demonstrated in other platforms such as InP to the author's knowledge because of the relatively high index of any type of (Al)InGaAs(P) lower cladding compared to negative TO materials. New materials data for  $TiO_2$  are presented with a realistic projection of both the promise and pitfalls of the material. More generally, novel athermal laser designs are presented enabled by athermal waveguides in a heterogeneous III-V on Si platform.

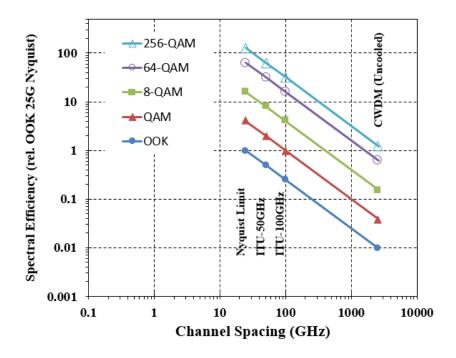

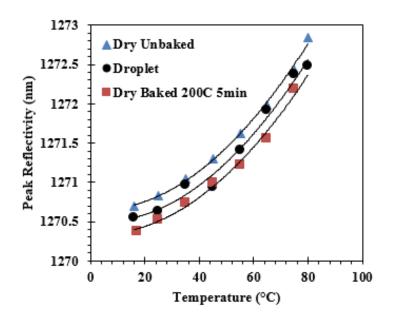

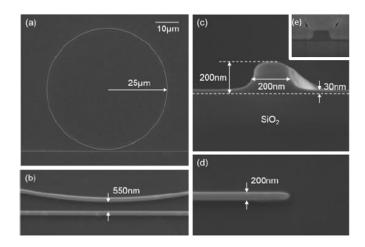

This research is important because the future is moving towards highly integrated uncooled systems. Such integration will not scale or achieve cost targets without the simplicity of athermal design. We project as much as a 100 fold improvement of spectral efficiency with the use of athermalized circuits over conventional CWDM solutions. Two approaches to achieve this are given. A novel TiO<sub>2</sub> core waveguide is presented with <3 pm/K thermal drift. A simple modification of a silicon rib waveguide by adding a TiO<sub>2</sub> cladding is demonstrated to reduce thermal drift of both gratings and rings at 1300 nm.

# 2.1 Applications and background for integrated athermal devices

There is a strong desire in a number of fields to develop photonic integrated circuits (PICs) that are *athermal*. What level of thermal insensitivity would be considered athermal is application specific, so the following examples should help illustrate what constitutes an athermal circuit. In general a wavelength selective element such as a multiplexer, ring, or grating is placed in the circuit to isolate one or more particular optical frequencies. Simply put, an athermal circuit should be able to maintain this filter response over a range of temperatures. The nature of conventional PICs is such that waveguides are comprised of dielectrics and semiconductors with positive thermo-optic coefficients on a substrate with a positive thermal expansion coefficient. This tends to cause a drift of all wavelength selective components to longer wavelengths with an increase in the temperature of the environment. Athermal circuits do not drift and therefore do not need to be held at a single temperature.

#### 2.1.1 Application examples

In sensing applications that use filters targeting particular molecular resonances, a desire to limit or engineer this thermal drift is very clear. For example, when monitoring molecular resonances that shift only slightly with air temperature an athermal circuit would have to have a filter bandwidth equal to the resonance shift across this small range and no more. A conventional (III-V or Si) circuit may require a filter bandwidth of 10-20 nm to capture such a resonance from 0-80 °C. Its ability to differentiate between molecules would suffer not withstanding the tremendous amount of noise such a wide filter could add to the signal. An SiO<sub>2</sub> based circuit could have as much as an order of magnitude less drift, but this could still be too much for many applications and you would lose the active component integration of III-V or Si. A preferred solution would passively maintain a narrow bandwidth no greater than the thermal drift of the resonance itself. In this chapter we present demonstrated thermal drift  $\sim 2$ pm/K, 40 times better than a Si filter and nearly an order of magnitude better than  $SiO_2$ . This holds the potential for similar significant reductions in signal to noise or integrated circuit stabilization for such sensors.