# **Evolution of Photonic Integrated Circuits**

## John E. Bowers

Department of Electrical and Computer Engineering, University of California Santa Barbara, Santa Barbara, California 93106, USA bowers@ece.ucsb.edu

**Abstract:** Photonic Integrated Circuits (PICs) are evolving rapidly for applications from interconnects to sensors. We present the evolution of four different platforms for photonic integration: pure III-V/InP, pure SOI (monolithic silicon photonics), III-V heterogeneously integrated on SOI (heterogeneous integration), and III-V epitaxially grown on silicon. Presently, thousands of optical devices are integrated into PICs to achieve multiterabit per second transceivers, LIDARs, and chemical sensors.

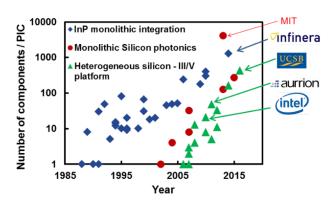

Photonic integrated circuits (PICs) are currently fueling high bandwidth density interconnection links, and are primed to serve other growth markets such as LIDAR and chip-scale wearable sensors. Various material platforms for photonic integration exist, each with their own unique advantages and shortcomings. Four different approaches are differentiated among these based on potential to deliver high performance with a monolithically integrated solution combining both active and passive functionalities, and the ability to scale at low cost with the expected growth of the overall photonic integrated circuit market: 1) pure III-V (InP), 2) silicon on insulator (SOI), 3) heterogeneous integration of III-V on SOI and 4) epitaxial growth of III-V on silicon. The level of integration (e.g. number of devices integrated onto one waveguide) for the first three approaches that has been demonstrated to date is summarized in Fig. 1. In the sections below, a brief description of each of the four approaches is given, along with some prominent commercial examples where applicable.

## 1) III-V/InP generic integration

Photonic integration on InP, whereby InP and related ternary or quaternary epitaxial stacks are grown on a common InP substrate for the subsequent fabrication of optoelectronic devices, provides a platform for complete monolithic integration of passive and active functions [1]. Active and passive interfaces are joined via vertical twin or single guide growths, quantum well intermixing, and/or butt-joint regrowth [1]. The most prominent foundry example is the joint European platform for InP-based components and circuits - JePPIX – which offers foundry services through Oclaro, the Fraunhofer Heinrich Hertz Institut (HHI) in Berlin, and the COBRA spinoff company SMART Photonics, located in Eindhoven. Infinera, Finisar, Lumentum and others all offer products based on InP PICs.

## 2) Monolithic silicon photonics (with Ge/Si laser or no integrated laser)

Silicon-on-insulator is the natural platform for mainstream silicon photonics, whereby the majority of optical functions are derived from devices constructed from the silicon device layer, while selective area epitaxy of germanium is used for photodetection. Many foundries today offer a relatively complete suite of technologies based on this platform including AIM Photonics, IMEC, Global Foundries, ST Microelectronics, among others. However, an integrated laser is missing from these processes. Commercial products based on this process have been released

Fig. 1. Photonic Moore's Law

by companies such as Acacia, Luxtera, Cisco, and PETRA, whereby an external III-V laser is coupled to the silicon photonic chip as the light source. Epitaxial growth of Ge-Si on Si for an integrated laser is not technically viable since the threshold currents are more than 1000x higher than the other three approaches, and low power is a key requirement for most datacom and telecom applications.

## 3) Heterogeneous Integration on SOI

Heterogeneous integration takes advantage of the silicon based processing in a monolithic silicon photonics process, but also utilizes III-V materials for some active optical functionalities such as gain, photodetection, and phase/amplitude modulation [2].

As an added benefit, integration of multiple epitaxial materials on a single PIC connected by a common Si waveguide is possible. A number of foundries such as CEA-LETI, IMEC and IME are currently exploring this process. Intel has recently released products formed by this technology, while Juniper Networks (Aurrion) and HPE are actively investing in the technology as well.

## 4) III-V epitaxially grown on silicon

The potentially lowest cost approach is to combine III-V with silicon via epitaxial growth, eliminating the need for III-V substrates altogether and taking advantage of the processing, testing, and packaging equipment for 300 mm substrates. There are two potential variations of this approach for the fabrication of PICs. One option is to couple light generated in a III-V section to passive photonic circuitry in silicon on an SOI substrate, which has been proposed previously [3]. The two disadvantages of this approach are the increased thermal resistance of the SOI substrate and coupling from the laser to the SOI waveguide through a relatively thick III-V base layer that is needed for defect reduction. Here, focus is given to an alternative approach where the entire PIC is fabricated from epitaxially deposited III-V layers, as is done in the case of integration on InP, but with the difference being the III-V layers are grown on a much cheaper and larger silicon substrate. Multiple bandgaps may be obtained from selective area growth, regrowth steps or intermixing as is done in the case of InP. This process is an active area of research both within academia as well as commercially by AIM, IMEC, and NTT, among others. In particular, many traditional CMOS foundries are exploring epitaxial growth of III-V on silicon as a "More-than-Moore" technology to extend the performance scaling of transistors past gate length scaling limits, and there is synergy in leveraging the same technology for photonics.

An important technological differentiator is the performance of the light source and how it is integrated[4-7]. Coupling losses can significantly reduce the efficiency of the overall circuit and limit performance scaling [5]. Offchip coupling of an external laser for monolithic silicon photonics typically results in 2-8 dB of coupling losses (including coupling from the laser to fiber and fiber to SOI). Integrated laser transitions can have much lower losses through proper butt-joint regrowth (0.1 dB) or well-designed taper transitions (0.2-0.5 dB). Semiconductor lasers from epitaxial III-V lasers on silicon are already showing reasonable performance, with additional room for improvement as this scheme provides the best natural heat-sinking for the laser.

Epitaxial growth of III-V on silicon stands to become a competitive solution as it is potentially the lowest cost solution and able to match or exceed the performance of the other approaches. While a fully functional PIC has not yet been demonstrated on this platform as most research efforts have gone towards engineering discrete devices, many building blocks are currently being set in place. Recent work on quantum dot lasers epitaxially grown on silicon have shown excellent performance with much improved lifetimes over previous iterations of epitaxial lasers on silicon [3, 8-9]; however, commercially acceptable lifetimes have not yet been demonstrated. Recently, several demonstrations of similar lasers grown on on-axis (001) CMOS compatible silicon substrates with no germanium or offcut have been reported [10-11]; and epitaxially grown photodetectors on silicon have been demonstrated with good performance [12]. Under the American Institute for Manufacturing (AIM) Integrated Photonics, work is ongoing to develop modulators as well as photodetectors from III-V materials epitaxially grown on silicon, improve laser performance on this platform, transfer the growth processes to 300 mm wafers, and accumulate data for a process design kit (PDK).

#### References

- [1] M. Smit et al., "An introduction to InP-based generic integration technology," Semicond. Sci. Technol., 29, 2014. [2] T. Komljenovic et al., "Heterogeneous Silicon Photonic Integrated Circuits." *Journal of Lightwave Technology*, **34**, 2016.

- [3] A. Y. Liu, S. Srinivasanan, J. Norman, A. C. Gossard, J. E. Bowers, "Quantum dot lasers for silicon photonics." Photon. Res. 3, B1-B9 (2015).

- [4] J. E. Bowers, J. Bovington, A. Y. Liu, A. C. Gossard, "A path to 300 mm hybrid silicon photonic integrated circuits," OFC 2014.

- [5] M. J. R. Heck, and J. E. Bowers, "Energy Efficient and Energy Proportional Optical Interconnects for Multi-Core Processors: Driving the Need for On-Chip Sources." IEEE J. Sel. Top. Quant. Electron., 20, 2014.

- [6] G. Kurczveil, P. Pintus, M. J. R. Heck, J. D. Peters, and J. E. Bowers, "Characterization of Insertion Loss and Back Reflection in Passive Hybrid Silicon Tapers." IEEE Photonics Journal, 5, 2013.

- [7] B. R. Koch, et al., "Integrated Silicon Photonic Laser Sources for Telecom and Datacom." OFC 2014.

- [8] A. Y. Liu et al., "High performance continuous wave 1.3 µm quantum dot lasers on silicon." Appl. Phys. Lett., 104, 2014.

- [9] S. Chen, et al. "Electrically pumped continuous-wave III-V quantum dot lasers on silicon." Nat. Photon. 10, 307-311 (2016).

- [10] A. Y. Liu et al., "Electrically pumped continuous-wave 1.3 µm quantum-dot lasers epitaxially grown on on-axis (001) GaP/Si," Optics Letters, 42, 2017.

- [11] Y. Wan et al., "Quantum dot lasers grown on (001) Si substrate for integration with amorphous Si waveguides," OFC 2017

- [12] Y. Geng, et al. "High-Speed InGaAs Photodetectors by Selective-Area MOCVD toward Optoelectronic ICs," IEEE JSTQE, 20, 2014.