## UNIVERSITY OF CALIFORNIA

#### Santa Barbara

## Silicon Evanescent Lasers

A Dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Electrical and Computer Engineering

by

Alexander Wei-Liang Fang

Committee in charge:

Professor John E. Bowers, Chair

Professor Nadir Dagli

Professor Evelyn Hu

Dr. Mario J. Paniccia

Dr. Richard Jones

March 2008

The dissertation of Alexander Wei-liang Fang is approved.

Dr. Richard Jones

Dr. Mario Paniccia

Professor Nadir Dagli-

Professor Evelyn Hu

Professor John E. Bowers, Committee Chair

March 2008

Silicon Evanescent Lasers

Copyright © 2008

by

Alexander Wei Liang Fang

#### **ACKNOWLEDGEMENTS**

I have always found the acknowledgement section of dissertations to be one of the most interesting to read since it gives a small glimpse of the author's journey to this stage in their life and the people, without whom, this destination would be unreachable. I am in debt to so many people for providing me with inspiration, emotional support, and technical guidance that has led to the completion of this period of my life.

I would first like to thank my loving parents Jean, Peter, and Josephine, my siblings, Phyllis and Eugene, and my grandmother, Yun-Hsia Fang, for being patient with me and believing in me while I spent the first 3 out of 6 years of my college career failing courses and trying to figure out what I wanted to do in life.

Next I'd like to thank my advisor, John Bowers, for taking me in as his student and giving me with the opportunity to work in his research group. During these past 4.5 years, John has provided an environment that not only helped me grow technically as a researcher, but also as a person. His work hard, play hard mentality is instilled in each of his students, and I am privileged to be one of his students.

In addition to Dr. Bowers, I'd like to acknowledge my committee members.

Professor Nadir Dagli's and Professor Evelyn Hu's wealth of knowledge in optoelectronics and semiconductor fabrication have been invaluable to this research. Dr. Richard Jones' mentorship and scrutiny of results has molded me into

the researcher I am today. Dr. Mario Paniccia's vision has allowed me to go to "the superbowl" with him on the silicon Raman laser project, and the silicon evanescent laser project, making graduate school a truly memorable experience.

I would like to give special thanks Hyundai Park. The development of the silicon evanescent platform was only possible through the synergy of our complementary skill set with Hyundai bringing the brains and with me bringing the humor. I'd like to think that we both rubbed off on each other and I was able to steal some of his brains.

I would also like to thank the rest of the Bowers' group during my time here at UCSB: Gehong, Manish, Geske, Staffan, Garrett, Gan, Hubert, Raja, Satoshi, Emily, Brian Koch, Ying-Hao, Hui-wen, Di, Andy, Brian Mcskimming, Matt, Je-Hyeong, Ashok, Siddharth, and Jock. Anand Ramaswamy should get special recognition for being the target for all my evil plots, and living to tell about them.

The Bowers' group assistants: Kate Ferrian, Jasmine Young, Christina Zumenstein, and Christine Dillard-Herrera, without whom I would be in extreme debt, and be buried in paperwork that, in reality, I should have taken care of to begin with.

I'd like to thank all my colleagues at Intel in Santa Clara, and Israel: Haisheng Rong, Andrew Alduino, Ansheng Liu, Ling Liao, Jeffrey Tseng, Oded Cohen, Omri Raday, Hanan Bar and others.

None of the device fabrication would have been possible without the UCSB nanofabrication facility staff. Jack Whaley, Brian Thibeault, and the rest of the cleanroom staff are a key element of what makes UCSB a world class research institution. Don Freeborn deserves special recognition for dealing with the demanding group of processers known as the "UCSB wafer-bonders".

I'd also like to thank my friends, classmates, and collaborators from the Coldren, Mishra, Dagli, Blumenthal groups and back at home for assistance in research, stimulating conversations, and a high tolerance my extreme behavior: Jon Klamkin, Janet Chen, Erica Lively, Joe Summers, Milan Mashanovitch, John Mack, Chris Sarantos, Chris Schaake, Eric Snow, Chang-Soo Suh, Ric Lwin, Eric Liu, Vikrum Nijjar, Dave Fan, Damon Do, Vijay Kamath, Jerry Sublett, and others.

Finally I'd like to thank my fiancée, Angela Penn, for understanding and supporting me when I chose to be 2500 miles away from her in order to seek out my dreams at UCSB.

# This dissertation is dedicated to my family and fiancée

#### **CURRICULUM VITAE**

#### **ALEXANDER WEI-LIANG FANG**

Born October 26, 1979, Philadelphia, Pennsylvania

#### **EDUCATION**

Doctor of Philosophy in Electrical and Computer Engineering University of California, Santa Barbara, March 2008

Master of Science in Electrical and Computer Engineering University of California, Santa Barbara, December 2005

Bachelors of Science in Electrical Engineering San Jose State University, May 2003

#### **TECHNICAL EXPERIENCE**

*Intel Corporation – Photonics technology labs*July 2004 – January 2005

Lawrence Livermore National Laboratory – FALCON lab July 2003 – August 2003

#### MENTORING EXPERIENCE

San Jose State University –Senior Design Project Mentor August 2006 – December 2007

NSF NNIN REU Program – REU Mentor July 2006 – August 2006 July 2007 – August 2007

A.V.I.D. Program – Student Mentor/Tutor January 2003 – May 2003

### **PATENTS**

"Dual core corrugated Bragg grating," O. Cohen, R. Jones, D. Rubin, **A. W. Fang**, US Patent number 7292753, Issued 11/6/2007

"Electrically pumped hybrid semiconductor evanescent laser," **A. W. Fang,** H. Park, J. E. Bowers, M. Paniccia, R. Jones, O. Cohen, Filed 6/2006

#### **PUBLICATIONS**

Journal Papers

"A distributed feedback silicon evanescent laser," **A. W. Fang**, E. Lively, Y-H. Kuo, D. Liang, J. E. Bowers, *Optics Express*, Vol. 16, No. 7, pp. 4413-4419, 2008

"A racetrack mode-locked silicon evanescent laser," **A. W. Fang**, B. R. Koch, K. Gan, H. Park, R. Jones, O. Cohen, M. J. Paniccia, D. Blumenthal, J. E. Bowers, *Optics Express*, Vol. 16, No. 2, pp. 1393-1398, 2008

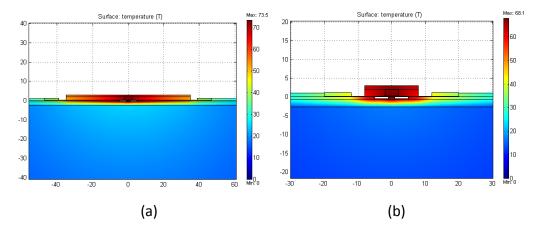

"Experimental and theoretical thermal analysis of a Hybrid Silicon Evanescent Laser," M. N. Sysak, H. Park, **A. W. Fang**, J. E. Bowers, R. Jones, O. Cohen, O. Raday, and M. Paniccia, *Optics Express*, Vol., 15 No. 23 Pg: 15041-15046, 2007

"A hybrid AlGaInAs-silicon evanescent preamplifier and photodetector," H. Park, Y.-H. Kuo, A. W. Fang, R. Jones, O. Cohen, M. J. Pannicia, J. E. Bowers, *Optics Express*, Vol. 15, No. 21, 2007

"Mode-locked silicon evanescent lasers," B. R. Koch, **A. W. Fang**, O. Cohen, and J. E. Bowers, *Optics Express*, Vol. 15, No. 18, pp. 11225-11233, 2007

"1310nm silicon evanescent laser," H.-H. Chang, A. W. Fang, M. N. Sysak, H. Park, R. Jones, O. Cohen, O. Raday, M. J. Paniccia, and J. E. Bowers, *Optics Express*, 15, 11466-11471, 2007

"Hybrid silicon integration," R. Jones, H. Park, **A. W. Fang**, J. E. Bowers, O. Cohen, O. Raday and M. J. Paniccia, *Journal of Materials Science: Materials in Electronics*, DOI 10.1007/s10854-007-9418-y, 2007

"Hybrid Si evanescent devices," **A. W. Fang**, H. Park, Y.-H. Kuo, R. Jones, O. Cohen, D. Liang, O. Raday, M. N. Sysak, M. J. Paniccia, and J. E. Bowers, *Materials Today*, 10, 7-8, 2007

"A hybrid AlGaInAs-silicon evanescent waveguide photodetector," H. Park, **A. W. Fang**, R. Jones, O. Cohen, O. Raday, M. N. Sysak, M. J. Paniccia, and J. E. Bowers, *Optics Express*, Vol. 15, Issue 10, pp. 6044-6052, 2007

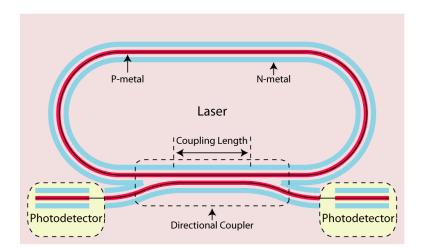

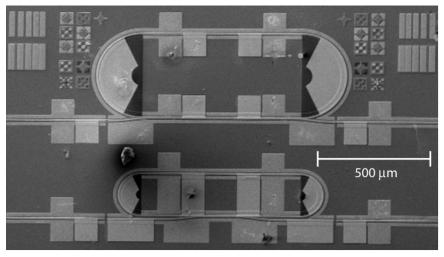

"Integrated AlGaInAs-silicon evanescent race track laser and photodetector," **A. W. Fang**, R. Jones, H. Park, O. Cohen, O. Raday, M. J. Paniccia, and J. E. Bowers, *Optics Express*, Vol. 15, Issue 5, pp. 2315-2322, 2007

"A Hybrid AlGaInAs-Silicon Evanescent Amplifier," H. Park, **A. W. Fang**, O. Cohen, R. Jones, M. J. Paniccia, J. E. Bowers, *IEEE Photonics Technology Letters*, Vol. 19, No. 4, 2007

"Design and Fabrication of Optically Pumped Hybrid Silicon-AlGaInAs Evanescent Lasers," H. Park, **A. W. Fang**, O. Cohen, R. Jones, M. J. Paniccia, J. E. Bowers, *IEEE Journal of Selected Topics in Quantum Electronics*, Vol. 12, Part 2, page 1657-1663, 2006

"Electrically pumped hybrid AlGaInAs-silicon evanescent laser," **A. W. Fang**, H. Park, O. Cohen, R. Jones, M. J. Paniccia, and J. E. Bowers, *Optics Express*, 14, 9203-9210, 2006

"A Continuous-Wave Hybrid AlGaInAs–Silicon Evanescent Laser," **A. W. Fang**, H. Park, R. Jones, O. Cohen, M. J. Paniccia, J. E. Bowers, *IEEE Photonics Technology Letters*, Vol 18, Issue 10, pg 1143-1145, 2006

"Hybrid Silicon Evanescent Laser Fabricated With a Silicon Waveguide and III-V Offset Quantum Wells," H. Park, **A. W. Fang**, S. Kodama, and J. E. Bowers, *Optics Express*, 13, 9460-9464, 2005

"A Continuous-Wave Raman Silicon Laser," H. Rong, R. Jones, A. Liu, O. Cohen, D. Hak, **A. W. Fang**, M. Paniccia, *Nature*, Vol. 433, Pg. 725 - 728, 2005

"Net Continuous Wave Optical Gain in a Low Loss," H. Rong, R. Jones, A. Liu, O. Cohen, D. Hak, **A. W. Fang**, M. Paniccia, *Optics Express*, Vol. 13, No. 2, Pg. 519 - 525, 2005

"An All-Silicon Raman Laser," H. Rong, A. Liu, R. Jones, O. Cohen, R. Nicolaescu, A. W. Fang, M. Paniccia, *Nature*, Vol. 433, Pg. 292 - 294, 2005

### Conference Papers

"Integrated Hybrid Lasers and Amplifiers on a Silicon Platform," R. Jones, M. N. Sysak, H. Park, **A. W. Fang**, H.-H. Chang, Y.-H. Kuo, J. E. Bowers, O. Raday, O. Cohen, Optical Fiber Communications Conference (OFC) 2008, San Diego, CA OWM1, 2008

"Distributed Feedback Silicon Evanescent Laser," **A. W. Fang**, E. Lively, Y.-H. Kuo, D. Liang, J. E. Bowers, Optical Fiber Communications Conference (OFC) 2008, San Diego, CA postdeadline session PDP15, 2008

"All-Optical Clock Recovery with Retiming and Reshaping Using a Silicon Evanescent Mode-Locked Ring Laser," B. R. Koch, **A. W. Fang**, H. N. Poulsen, H. Park, D. J. Blumenthal, and J. E. Bowers, R. Jones and M. J. Paniccia, and O. Cohen, Optical Fiber Communications Conference (OFC) 2008, San Diego, CA Paper OMN1 (Invited), 2008

"Experimental and Theoretical Analysis of Thermal Impedance in a Hybrid Silicon Evanescent Laser," M. N. Sysak, H. Park, **A. W. Fang**, J. E. Bowers, R. Jones, O. Cohen, O. Raday, and M. Paniccia, LEOS annual meeting 2007, ThR2, 2007

"Hybrid AlGaInAs-silicon evanescent racetrack laser," **A. W. Fang**, R. Jones, H. Park, O. Cohen, M. J. Paniccia, and J. E. Bowers, LEOS annual meeting 2007, ThR1 (Invited), 2007

"Hybrid III-V and IV lasers and amplifiers," J. E. Bowers, H. Park, **A. W. Fang**, Y.-H. Kuo, R. Jones, O. Cohen, O. Raday, M. J. Paniccia, European Conference on Optical Communications (ECOC) 2007, Paper 9.2.1 (Invited), 2007

"A 40 GHz Mode Locked Silicon Evanescent Laser," B. R. Koch, **A. W. Fang**, H.-H. Chang, H. Park, Y.-H. Kuo, R. Jones, O. Cohen, O. Raday, M. J. Paniccia, J. E. Bowers, 4th International Conference on Group IV Photonics, Tokyo Japan, wb1 (invited), 2007

"1310nm Silicon Evanescent Laser," H.-H. Chang, **A. W. Fang**, M. N. Sysak, H. Park, Y.-H. Kuo, R. Jones, O. Cohen, O. Raday, M. J. Paniccia, J. E. Bowers, 4th International Conference on Group IV Photonics, Tokyo Japan, wb3, 2007

"Silicon Evanescent Racetrack Laser," **A. W. Fang**, H. Park, J. E. Bowers, R. Jones, M. J. Paniccia, O. Cohen, O. Raday, Frontiers in Optics 2007, San Jose, California, FTuM3(invited), 2007

"Integrated AlGaInAs-silicon evanescent racetrack laser and photodetector," **A. W. Fang**, R. Jones, H. Park, O. Cohen, O. Raday, M. J. Paniccia, J. E. Bowers, Optics East 2007, Proc. of SPIE Vol. 6775 67750P-1 (Invited), 2007

"Silicon Evanescent Amplifiers," J. E. Bowers, H. Park, **A. W. Fang**, R. Jones, M. J. Paniccia, O. Cohen, CLEO Pacific Rim 2007, Seoul, Korea, FA1-2 (invited), 2007

"Hybrid Silicon Integration," R. Jones, H. Park, **A. W. Fang,** J. E. Bowers, O. Cohen, O. Raday, and M. J. Paniccia, ICOOPMA (The International Conference on Optical, Optoelectronic and Photonic Materials and Applications), London, 2007

"Integrated Optical Amplifiers on Silicon Waveguides," J. E. Bowers, H. Park, Y.-H. Kuo, A. W. Fang, R. Jones, M. J. Paniccia, O. Cohen, O. Raday, IPNRA 2007, invited paper, ITuG1, 2007

"Integrated Hybrid Silicon Evanescent Racetrack Laser and Photodetector," **A. W. Fang**, R. Jones, H. Park, O. Cohen, O. Raday, M. J. Paniccia, J. E. Bowers, 12th OptoElectronics and Communications Conference, Yokohama Kanagawa, Japan (Invited), 2007

"A hybrid silicon evanescent photodetector," H. Park, **A. W. Fang**, R. Jones, O. Cohen, O. Raday, M. N. Sysak, M. J. Paniccia, J. E. Bowers, Device Research Conference (DRC 2007), Notre Dame, IN, 2007

"Low Temperature Wafer Bonding for III-V Si Photonic Integrated Circuits," D. Liang, H. Park, A. W. Fang and J. E. Bowers, Electronic Materials Conference, paper L3, 2007

"Hybrid Silicon Evanescent Photonic Integrated Circuit Technology," J. E. Bowers, A. W. Fang, H. Park, R. Jones, O. Cohen, and M. J. Paniccia, CLEO 2007, CTuQ1, Baltimore MD, 2007

"High speed data amplification using hybrid silicon evanescent amplifier," Y.-H. Kuo, H. Park, A. W. Fang, J. E. Bowers, R. Jones, M. Paniccia, O. Cohen, CLEO 2007, CTull1, 2007

"An electrically pumped hybrid silicon evanescent amplifier," H. Park, **A. W. Fang**, R. Jones, O. Cohen, J. E. Bowers, Optical Fiber Communication Conference (OFC 2007), OTuD2, Anaheim CA, 2007

"Hybrid Silicon Evanescent Laser in a Silicon-on-Insulator Waveguide," J.E. Bowers, **A. W. Fang**, H. Park, R. Jones, O. Cohen, M. J. Paniccia, Optical Fiber Communication Conference (OFC 2007), OTuK4, Anaheim CA, 2007

"High Temperature Silicon Evanescent Lasers," J. E. Bowers, H. Park, **A. W. Fang**, R. Jones, O. Cohen, M. J. Paniccia, Photonics West 2007 (PW 2007), Proceedings of SPIE, Vol. 6485, invited paper, 2007

"Scalable Wafer Bonding for Active Photonic Devices on Silicon," J. E. Bowers, H. Park, A. W. Fang, R. Jones, O. Cohen, M. Paniccia, LEOS Annual Meeting, TuC1 (Invited), 2006

"40 C Continuous-Wave Electrically Pumped Hybrid Silicon Evanescent Laser," H. Park, **A. W. Fang**, R. Jones, O. Cohen, M. J. Paniccia, and J. E. Bowers, International Semiconductor Laser Conference 2006 (ISLC 2006), post deadline paper, 2006

"Silicon Evanescent Lasers and Amplifiers," J. E. Bowers, **A. W. Fang**, H. Park, R. Jones, O. Cohen, M. J. Paniccia, Group IV Photonics Conference 2006 (GFP2006), Invited Paper, ThB1, 2006

"Design of Hybrid Silicon Evanescent Amplifiers," J. E. Bowers, H. Park, **A. W. Fang**, R. Jones, O. Cohen, M. J. Paniccia, COIN 2006, Jeju Korea, 2006

"Hybrid silicon evanescent lasers," J. E. Bowers, **A. W. Fang**, H. Park, O. Cohen, R. Jones, M. J. Paniccia, Device Research Conference 2006 (DRC 2006), (invited paper) University Park, PA, 2006

"A Technology for Integrating Active Photonic Devices on SOI Wafers," J. E. Bowers, H. Park, A. W. Fang, R. Jones, O. Cohen, and M. J. Paniccia, Indium Phosphide and Related Materials Conference (IPRM 2006), Princeton, NJ, Invited Paper, 2006

"SOI-based monolithic integration of SiON and Si planar optical circuits," O. Cohen, R. Jones, O. Raday, A. W. Fang, N. Izhaky, D. Rubin, M. Paniccia, Photonics Europe, 2006

"An optically pumped silicon evanescent laser operating continuous wave at 60 <sup>o</sup>C," H. Park, A. W. Fang, R. Jones, O. Cohen, M. J. Paniccia, and J. E. Bowers, Optical Fiber Communication Conference (OFC 2006), paper OWH2, 2006

"Heterogeneous Integration of Silicon and AlGaInAs for a Silicon Evanescent Laser," **A. W. Fang**, H. Park, R. Jones, O. Cohen, M. J. Paniccia, J. E. Bowers, Proc. of SPIE 6133, (Photonics West 2006), Vol. 6133, 61330W, San Jose, CA, Invited Paper, 2006

"An Optically Pumped Silicon Evanescent Laser," **A. W. Fang**, H. Park, S. Kodama, J. E. Bowers, The 31st European Conference on Optical Communications (ECOC 2005), SECC, Glasgow, Scotland, 2005

"Novel Laser Diode Structure consisting of a Si Waveguide and Compound-Semiconductor MQW Layers for Si Platform Integration," S. Kodama,, H. Park, **A. W. Fang** and J. E. Bowers, International Conference on Solid State Devices and Materials, Kobe, Japan, 2005

"Integration of SiON Gratings with SOI," R. Jones, O. Cohen, H. Chan, D. Rubin, **A. W. Fang** and M. Paniccia, GFP 2005 2nd International Conference on Group IV Photonics, Antwerp, Belgium, 2005

## **ABSTRACT**

## Silicon Evanescent Lasers

by

## Alexander Wei-Liang Fang

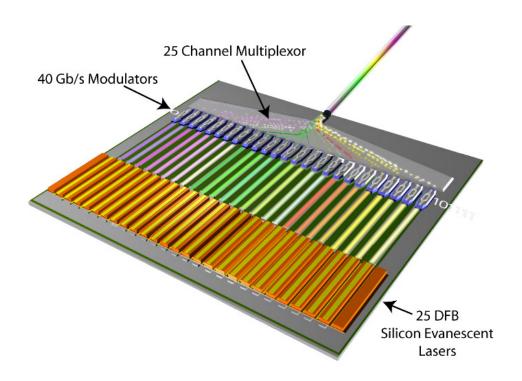

Silicon photonics has seen much advancement in recent years, driven by the potential to break the cost barrier of optoelectronics through leveraging the low cost manufacturing infrastructure of the CMOS electronics industry. Silicon Raman lasers have been demonstrated, but an electrically pumped laser made of pure silicon has yet to be realized. Hybrid integration approaches that consist of die bonding prefabricated compound semiconductor lasers to silicon waveguides fall short of the requirements needed for high volume silicon photonic integration manufacturing due to the high precision alignment bonding techniques, leading to large variations in coupling losses and scalability limitations. In this dissertation, we present the silicon evanescent laser, an electrically pumped laser architecture that consists of III-V layers bonded to silicon waveguide optical cavities. The optical mode lies primarily in the low loss silicon waveguide while obtaining optical gain through evanescent coupling into the III-V region. Since lateral confinement is controlled by the silicon waveguide fabrication, this self aligned process allows for thousands of lasers to be fabricated on a silicon die in a single bond step. Subsequent processing is done on the III-V but can be conducted using standard lithographic based processing techniques. We have demonstrated electrically pumped Fabry-Perot lasers, racetrack resonator lasers under continuous wave and mode locked operation and distributed feedback (DFB) lasers utilizing this platform.

# **TABLE OF CONTENTS**

| 1. | Introduction 1.1. Silicon Photonics 1.2. Silicon Photonic Integrated Circuit Laser Sources 1.3. Silicon Evanescent Device Concept 1.4. This Dissertation                                                                                                                                                                                                             | 1<br>1<br>3<br>5<br>6                        |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 2. | Silicon Evanescent Laser Design, Fabrication, and Proof of Concept 2.1. Silicon Evanescent Waveguide Design 2.2. Device Fabrication 2.3. Proof of Concept – Optically Pumped Silicon Evanescent Lasers 2.4. Summary                                                                                                                                                  | 9<br>10<br>17<br>29<br>37                    |

| 3. | Electrically Pumped Silicon Evanescent Lasers – Fabry Perot Lasers  3.1. Pulsed Lasing Device Structure  3.2. Pulsed Lasing Operation  3.3. Continuous Wave Device Structure - Lateral Current Confinement  3.4. Continuous Wave Lasing  3.5. Thermal Analysis  3.6. Second Generation Fabry-Perot Lasers  3.7. Thermal Modeling of Fabry-Perot Lasers  3.8. Summary | 40<br>43<br>48<br>51<br>61<br>63<br>67<br>69 |

| 4. | Electrically Pumped Silicon Evanescent Lasers – Racetrack Ring Lasers 4.1. Racetrack Laser Design 4.2. Continuous Wave Lasing 4.3. Mode Locked Racetrack Lasers 4.4. Summary                                                                                                                                                                                         | 72<br>73<br>84<br>89<br>97                   |

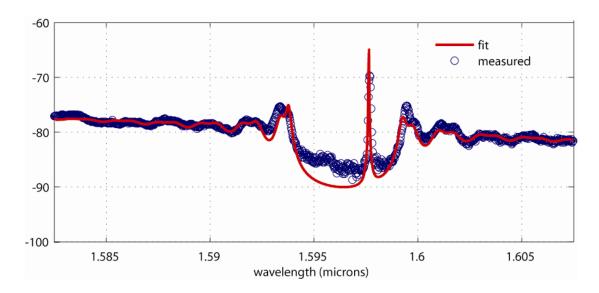

| 5. | Distributed Feedback Silicon Evanescent Lasers 5.1. Bragg Grating Design and Fabrication 5.2. Distributed Feedback Silicon Evanescent Lasers 5.3. Summary                                                                                                                                                                                                            | 100<br>102<br>105<br>115                     |

| 6. | Conclusions and Future Work 6.1. Summary 6.2. Future Directions                                                                                                                                                                                                                                                                                                      | <b>117</b><br>118<br>121                     |

| A. | Appendix a. Electrically Pumped SEL Process Follower                                                                                                                                                                                                                                                                                                                 | <b>129</b><br>129                            |

# **Chapter 1 - Introduction**

## 1.1 - Silicon Photonics

Silicon is the material of choice for most applications in the world of electronics. People have spent decades perfecting the understanding of silicon and building up a fabrication infrastructure that is unsurpassed by any other semiconductor material system that allows for the high yield and high volume manufacturing of electronic systems. In recent years, a lot of attention in optoelectronics has shifted from compound semiconductor based material systems to silicon.

Optical communication systems are still predominantly put together on the component level, similar to electronic systems of the 1950s where resistors, capacitors, and transistors were soldered together individually. This keeps the cost of optical communication systems high, due to assembly and packaging costs. It also limits the scalability of the number of optical components within a system. As a result, optoelectronic systems have remained in markets that are high performance, and low volume, such as long haul wide area networks (WANs) and metro area networks (MANs) that connect cities digitally throughout the world, serving as the backbone of the internet, and telephone traffic where the cost of high bandwidth optical links can be justified. As our society moves further into the digital era, the demand for greater bandwidth drives the push for optical communication links in to

our homes. The supply for this demand can only happen if the cost barrier is broken, allowing for high volume deployment of optical links. The integration of components onto a single chip revolutionized electronics and the hope is to use integration as an enabler for a similar revolution in optoelectronics. Silicon based photonics strives to further reduce the cost of photonic integrated circuits by utilizing the fabrication infrastructure of silicon CMOS electronics to realize high yield manufacturing while reducing the costs associated with running dedicated photonic fabrication lines. At first glance, silicon does not have much in its toolbox for optoelectronics. First of all, it is an indirect band gap semiconductor leading to inefficient band to band light emission. Secondly, the inversion symmetry of silicon's crystal structure results in the absence of the linear electro-optic effect [1]. Thirdly, the bandgap of silicon is 1.12 eV which corresponds to absorption of wavelengths of ~ 1.1 microns and shorter making it poor for light detection at the telecommunication wavelength windows at 1.3 microns and 1.55 microns [2]. Even with these properties stacked against it, the potential to leverage silicon's high volume, low cost manufacturing infrastructure as a means to produce low cost photonic systems that can finally break the cost barrier of photonic systems has driven researchers to press on and has resulted in great strides in the field of silicon photonics. Low loss waveguides in silicon have been demonstrated with losses on the order of ~0.3 dB/cm (0.075 cm<sup>-1</sup>) [2]; over an order of magnitude improvement over their indium phosphide counterparts (~4 - 40 dB/cm, ~1 - 10 cm<sup>-1</sup>). Silicon modulators have broken the previous 20 MHz bandwidth limit with bandwidths of 30 GHz making them viable for high speed communication systems [4][5]. New ultra compact modulators utilizing ring resonators and pre-emphasized signals have shown modulation speeds of 18 Gb/s while only occupying  $12 \times 12 \, \mu m^2$  allowing for dense integration [6]. High speed silicon germanium photodetectors have been demonstrated in the 1550 nm [7] and the 1310 nm regime with data rates of 40 Gb/s [8]. These developments have given silicon almost everything it needs in the photonic toolbox to be used as a platform for photonic integrated circuits. The only missing piece is and electrically pumped laser on silicon.

# 1.2 - Silicon Photonic Integrated Circuit Laser Sources

Although optically pumped silicon lasers have been demonstrated by utilizing stimulated Raman scattering (SRS) in silicon waveguides, there is no clear path to realizing an electrically pumped laser out of pure silicon [9][10].

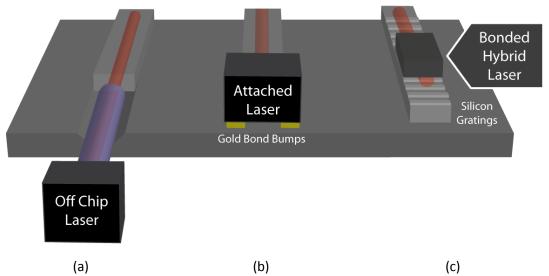

Figure 1-1 illustrates a few methods for getting light onto a silicon photonic integrated circuit. The first approach involves using an off chip laser that is fiber coupled to the silicon chip (Figure 1-1a). Once the light is on the silicon, it can be modulated or detected via silicon modulators and detectors. Although Raman scattering can be used to achieve narrowband amplification (10 nm) via a high power pump laser [11], true broadband (~40 nm) amplification at is currently unavailable with this method. This method can be thought of as an optical power

supply. In order to minimize fabrication costs, v-grooves or other passive alignment techniques should be used in this approach to reduce packaging costs.

The second approach is taking prefabricated compound semiconductor lasers and bump bonding them to silicon waveguides (Figure 1-1b). Since the waveguide in the laser and the waveguide of the silicon is defined prior to bonding, tight alignment (< micron) needs to be made during the bonding process to ensure efficient coupling.

Figure 1-1 – Three methods to supply laser light to a photonic integrated circuit on silicon: (a) fiber coupling off chip lasers to silicon waveguides, (b) die attaching prefabricated III-V lasers, and (c) hybrid integration of III-V materials and silicon to form a hybrid laser.

The third approach is to transfer thin crystalline films to the silicon, and process them with standard lithographic and etching processes to define the device structure (Figure 1-1c). This approach removes the high precision alignment step from the bonding step, and moves it to lithographic steps, allowing for high precision alignment with standard semiconductor fabrication tools.

Wada *et al.* first demonstrated a III-V Fabry-Perot laser, fabricated on a silicon wafer via direct wafer bonding [12]. The optical mode of this laser lies entirely in the III-V layers, 1.5 microns away from the bonded interface and would require special coupling schemes in order to integrate it with photonics imbedded in a layer on the silicon. Although, the silicon served only as a carrier medium, this demonstration shows that the quality of thin crystalline III-V materials transferred to silicon can be maintained to create electrically driven lasers on silicon.

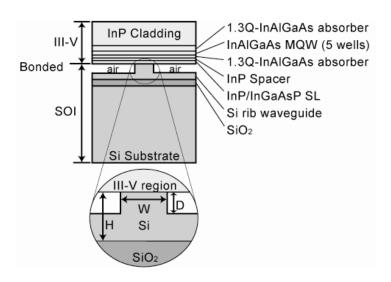

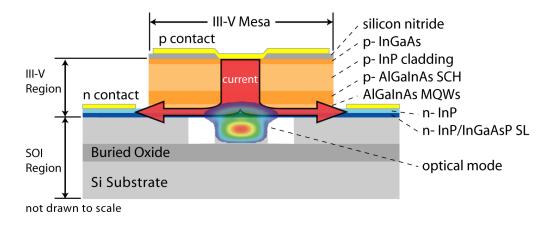

# 1.3 - Silicon Evanescent Device Concept

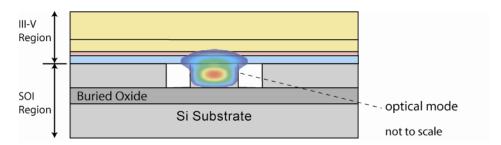

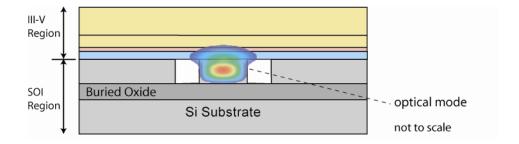

The silicon evanescent waveguide structure also utilizes thin films crystalline III-V films transferred to silicon, but in this structure, the optical mode lies primarily in the silicon waveguide region and is evanescently coupled through the bonded interface and a thin InP layer in the III-V region to a set of quantum wells (Figure 1-2). This allows for high coupling efficiency to other passive silicon devices; typically between -3 dB and -1 dB. Since the waveguide definition is done in the silicon region, the cavity is defined by processing on the silicon through the introduction of ring resonator topographies or the use of Bragg reflectors to create distributed feedback (DFB) or distributed Bragg reflector (DBR) lasers. Although we focus

primarily on the development of lasers based on this platform, this structure is also useful for amplifiers [13], photodetectors [14], and modulators [15].

Figure 1-2 – Silicon evanescent waveguide structure consisting of III-V active layers bonded to a silicon on insulator (SOI) waveguide.

## 1.4 - This Dissertation

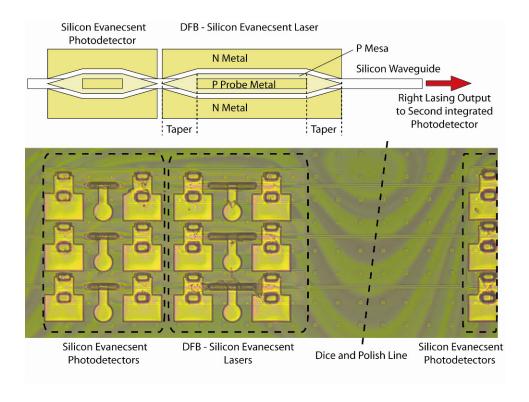

This dissertation focuses on the development of the silicon evanescent device platform to realize electrically pumped lasers on silicon. Chapter 2 describes the modal properties of silicon evanescent device platform along with the fabrication of these devices. The demonstration of optically pumped Fabry Perot silicon evanescent lasers is presented at the end of this chapter as a proof of concept. Chapter 3 describes the development of the current injection scheme and the realization of electrically pumped Fabry Perot silicon evanescent lasers. This chapter includes two generations of devices with an analysis of the device thermal performance. Chapter 4 presents the design and demonstration of racetrack silicon evanescent lasers with integrated photodetectors in order to demonstrate lasers that do not rely on facet preparation and to illustrate the use of silicon patterning to

define the laser cavity. These lasers operate continuous wave and under mode locked operation. Distributed feedback silicon evanescent lasers are presented in Chapter 5 where the gratings are fabricated in the silicon waveguide to yield single wavelength outputs for wavelength division multiplexing applications. Chapter 6 concludes this dissertation with a discussion on the future development of silicon evanescent lasers.

# References

- [1] G. T. Reed & C. E. J. Png, "Silicon optical modulators," Mater. Today, 8, 40–50 (2005)

- [2] B. Streetman, S. Banerjee, *Solid State electronic Devices*, New Jersey: Prentice Hall, pp. 524. (2000)

- [3] H. Rong, R. Jones, A. Liu, O. Cohen, D. Hak, A. W. Fang, M. Paniccia, "A continuous-wave Raman silicon laser." Nature, 433, 725–727 (2005)

- [4] A. Liu et al., "A high-speed silicon optical modulator based on a metal-oxidesemiconductor capacitor," Nature, 427, 615–618 (2004)

- [5] A. Liu et al., "High-speed silicon modulator for future VLSI interconnect," Indium Phosphide and Rel. Mat. Conf. (2007)

- [6] S. Manipatruni, Q. Xu, B.S. Schmidt, J. Shakya, and M. Lipson, "High Speed Carrier Injection 18 Gb/s Silicon Micro-ring Electro-optic Modulator," Lasers and Electro-Optic Society annual meeting (2007)

- [7] D. Ahn, C.-Y. Hong, J. Liu, W. Giziewicz, M. Beals, L. C. Kimerling, J. Michel, J. Chen, and F. X. Kärtner, "High performance, waveguide integrated Ge photodetectors," Opt. Express 15, 3916-3921 (2007)

- [8] T. Yin, R. Cohen, M. Morse, G. Sarid, Y. Chetrit, D. Rubin, M. Paniccia, "40Gb/s Ge-on-SOI Waveguide Photodetectors by Selective Ge Growth," Optical Fiber Communications Conference, OMK2 (2008)

- [9] O. Boyraz and B. Jalali, "Demonstration of a silicon Raman laser," Opt. Express 12, 5269-5273 (2004)

- [10] H. Rong, R. Jones, A. Liu, O. Cohen, D. Hak, A. W. Fang, M. Paniccia, "A continuous-wave Raman silicon laser." Nature, 433, 725–727 (2005)

- [11] D. R. Solli, P. Koonath, B. Jalali, "Broadband Raman amplification in silicon" Lasers and Electro-Optics Society Annual Meeting, 886-887 (2007)

- [12] H. Wada and T. Kamijoh, "Room-Temperature CW operation of InGaAsP Lasers on Si Fabricated by Wafer Bonding," IEEE Photon. Technol. Lett. 8, 173-175 (1996).

- [13] H. Park, A. W. Fang, O. Cohen, R. Jones, M. J. Paniccia, J. E. Bowers, "A Hybrid AlGaInAs-Silicon Evanescent Amplifier," IEEE Photon. Technol. Lett., 19, 4 (2007)

- [14] H. Park, A. W. Fang, R. Jones, O. Cohen, O. Raday, M. N. Sysak, M. J. Paniccia, and J. E. Bowers, "A hybrid AlGaInAs-silicon evanescent waveguide photodetector," Optics Express, Vol. 15, Issue 10, pp. 6044-6052, (2007)

- [15] Y.-H. Kuo, H.-W. Chen, J. E. Bowers, "A hybrid silicon evanescent electroabsorption modulator," Optical Fiber Communications Conference, (2008)

# Chapter 2 - Silicon Evanescent Device Design, Fabrication, and Proof of Concept

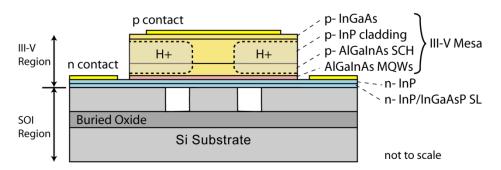

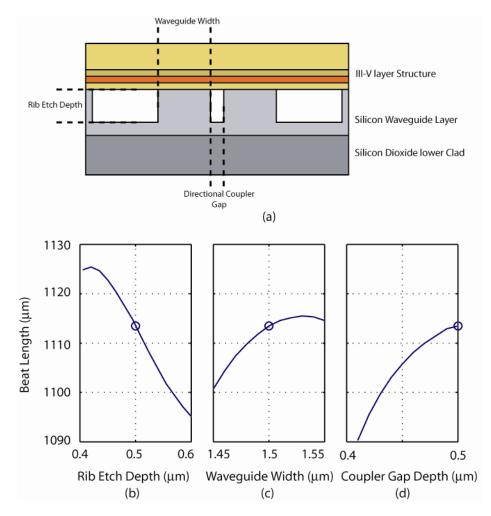

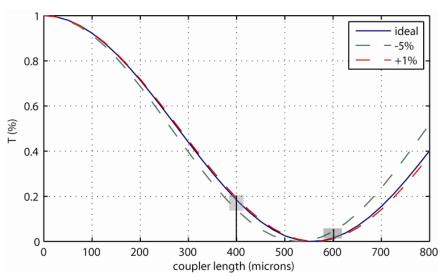

The silicon evanescent device structure consists of a III-V epitaxial active layer structure bonded to a silicon waveguide fabricated on a silicon on insulator (SOI) wafer. The optical mode lies primarily in the silicon waveguide region while part of the mode lies in the upper III-V region, as shown in Figure 2.1. The high modal overlap in the silicon region allows for efficient coupling into passive regions where the III-V layer is etched off, such as distributed feedback mirrors that may exist outside the gain region of the device, or other devices in a photonic integrated circuit that are composed entirely of silicon, such as modulators, multiplexers, etc. The close proximity of the III-V region, and in particular the quantum wells, to the silicon allows for efficient evanescently coupled gain. This chapter begins with a discussion on the design of this waveguide structure in the context of semiconductor lasers. Next, we describe the fabrication of the silicon evanescent lasers. This includes silicon waveguide processing, wafer bonding, and the processing of III-V materials after bonding. The chapter is concluded with a demonstration and brief analysis of optically pumped silicon evanescent lasers as a proof of concept of the device structure [1][2].

Figure 2.1 – Silicon evanescent device concept.

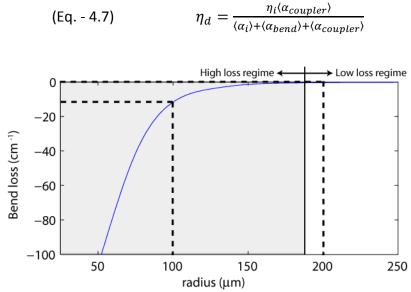

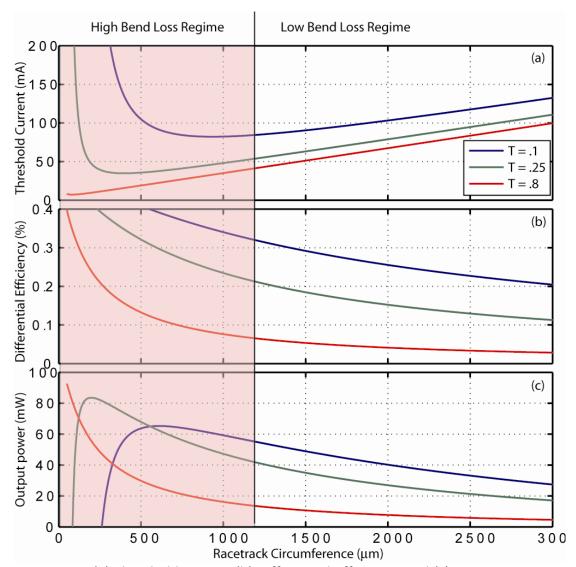

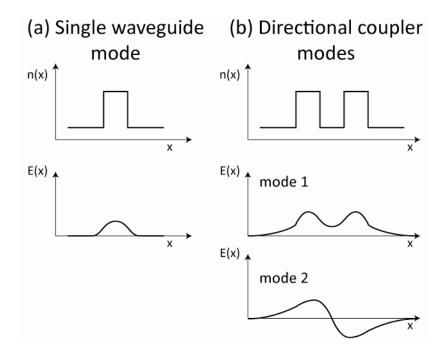

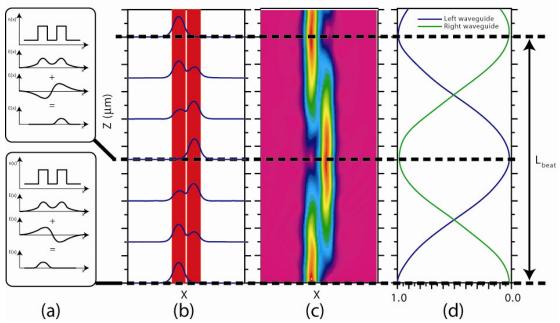

# 2.1 – Silicon Evanescent Waveguide Design

Several things are important when designing the waveguide for silicon evanescent lasers. First, we need to ensure that we have enough optical mode overlap with the active region to achieve sufficient optical gain for lasing. Second, we want to maximize the overlap in the silicon region such that the device can easily couple to non-hybrid regions that may help form the cavity, such as silicon gratings for distributed Bragg grating lasers, or other photonic devices on silicon. Finally, the waveguide design strongly affects the minimum bend radius a waveguide can undergo before bend loss becomes an issue. This factor is not important for linear lasers, but plays a large role in ring and racetrack lasers and will be discussed in Chapters 4 and 6.

We define the optical mode overlap, or confinement factor, in a given region in the transverse plane (x,y) as [3]:

(Eq - 2.1)

$$\Gamma = \frac{\iint_{region} E(x, y)^* E(x, y) dxdy}{\iint_{region} E(x, y)^* E(x, y) dxdy}$$

where E(x,y) is the electric field profile of the optical mode over the x-y plane. The confinement factor is a key design parameter for designing silicon evanescent lasers since it helps relate the amount of interaction the mode has with the gain material and helps give a ball park value for butt-coupling between hybrid and non-hybrid waveguide regions.

The threshold modal gain condition states that the lasing threshold occurs where the round trip gain equals the round trip losses. These losses originate from absorption and scattering during propagation through the waveguide and light coupled out of the cavity at facets or output couplers. For linear cavity lasers, this condition is expressed [4]:

(Eq - 2.2)

$$\langle g_{th} \rangle = \Gamma_{Quantum \ Well} g_{th} = \langle \alpha_i \rangle + \langle \alpha_{mirror} \rangle$$

(Eq - 2.3)

$$= \langle \alpha_i \rangle + \frac{1}{L_{Cavity}} \ln \frac{1}{\sqrt{r_1 r_2}}$$

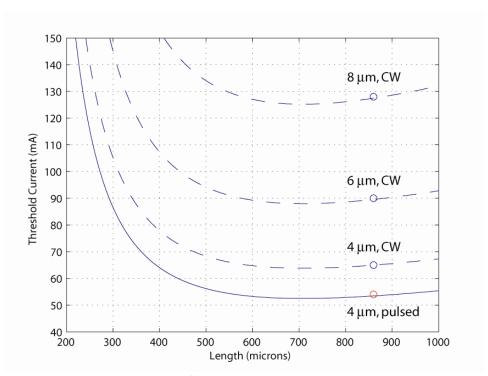

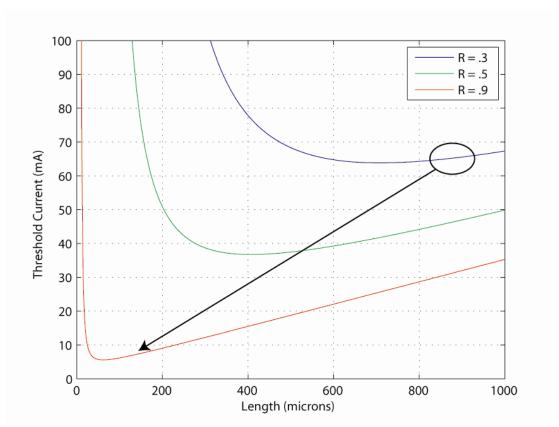

where  $g_{th}$  is the material gain at threshold, and  $\langle \alpha_i \rangle$  is the modal propagation loss. These values are on the order of 1000 cm<sup>-1</sup> and 16 to 40 cm<sup>-1</sup> for typical III-V lasers [5], respectively. The mirror loss,  $\langle \alpha_{mirror} \rangle$ , consists of the two facet reflectivities,  $r_1$  and  $r_2$ , and the cavity length,  $L_{cavity}$ . The facet reflectivity is roughly 0.53 (R = 0.3), between silicon and air based on Fresnel reflection [6]. The cavity length,  $L_{cavity}$ , is

designed to be  $\sim$  800  $\mu$ m long in order to keep the mirror loss below or equal to the modal loss. Substituting these values into Equation 2.2 and solving for  $\Gamma_{Quantum\ Well}$ , we find that the confinement factor in the quantum well,  $\Gamma_{Quantum\ Well}$ , should be at least 3% to achieve lasing. Although this condition is very rough, it gives us a good starting point on how to design these lasers. Ideally, there is an optimum design where confinement factors for the III-V and the silicon regions are decided to yield the desired lasing performance.

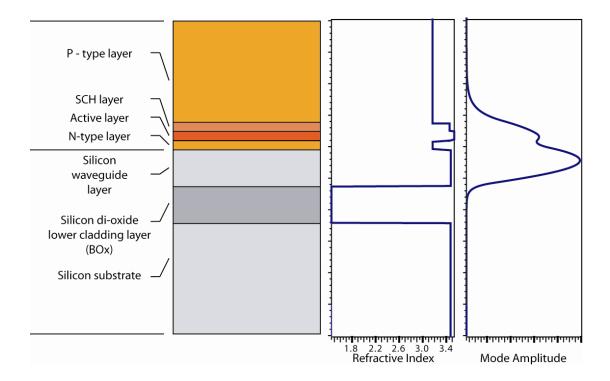

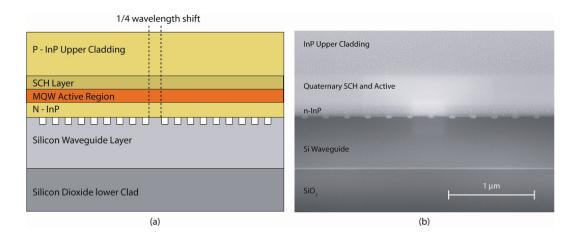

The 1-D layer structure is shown in Figure 2-2 along with the index profile, and mode amplitude profile of this structure. The mode has two lobes, with the main lobe lying in the silicon waveguide region, and the small second lobe lying in the SCH and active region. A thin N-type InP region with low index lies between these two regions and is used in this structure for vertical carrier confinement and as a current injection layer for electrically pumped devices. It is kept thin enough, that efficient evanescent coupling between the active region and silicon region can be achieved while being thick enough that current can flow through this layer without adding a substantial amount of series resistance.

Figure 2.2 – A 1-D diagram of the layer structure with the refractive index and the 1-D mode amplitude profile.

The waveguide has an upper waveguide cladding of P-type InP and a lower waveguide cladding of silicon dioxide. The silicon dioxide layer has an index of  $^{\sim}$  1.45 and needs to be sufficiently thick enough to prevent the evanescent coupling of the optical mode in the waveguide layer to the substrate modes. In this work we use a minimum buried oxide (BOx) thickness of 1  $\mu$ m, based on optical mode calculations of the evanescent field penetration depth, to maintain low loss.

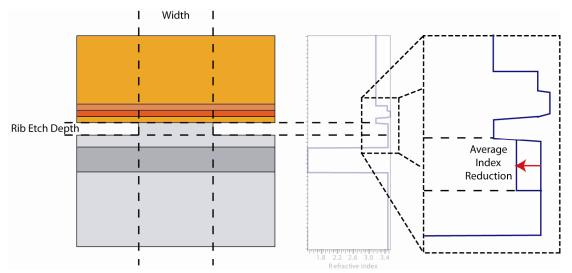

Figure 2.3 – A Diagram of the layer structure with the addition of lateral confinement in the silicon region. The average index profile is shown to the right.

Before diving into a full parameter scan of confinement factors with a mode solver, let's develop a qualitative understanding of how to manipulate the mode in the vertical direction. It is well understood that the mode profile will occupy regions with higher index [7]. Without lateral confinement, the confinement factor over the silicon region, and the quantum well region is modified by altering the silicon waveguide height and the SCH thickness where taller silicon heights pull the mode into the silicon, or greater SCH thicknesses pull the mode into the III-V region. We use a silicon height of 700 nm and an SCH thickness of 500 nm for optically pumped devices and 250 nm for electrically pumped devices and throughout this thesis. This leads to confinements in the silicon region and quantum well region of about ~60-45% and 3 - 8%, respectively. The remaining mode lies in the III-V region outside of the quantum wells.

Transverse optical confinement is achieved by etching a rib waveguide into the top silicon waveguide layer as shown in Figure 2.3. This leads to a reduction in the average lateral index as seen in the index profile vertical cross section (Figure 2.3). The strength of this reduction increases as rib waveguide width narrows. The narrower a waveguide is etched, the lower the average index in the silicon region, pushing the mode out to the III-V region.

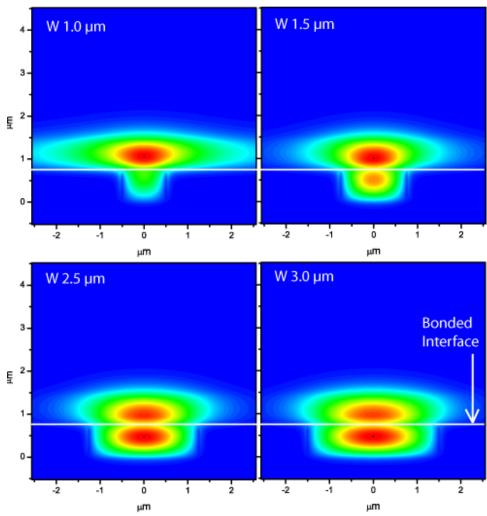

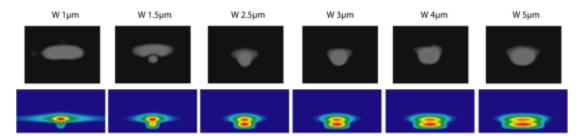

Figure 2.4 – Calculated mode profiles for fixed waveguide heights of 0.7  $\mu$ m and rib etch depths of 0.5  $\mu$ m. The waveguide width is varied from 1.0  $\mu$ m to 3.0  $\mu$ m to show the change in optical mode with waveguide width.

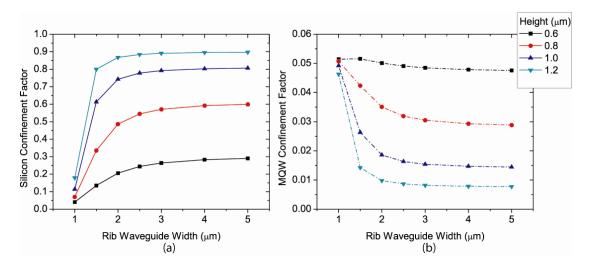

Figure 2.5 – (a) Silicon waveguide and (b) Multiple quantum well region confinement factors for an SCH thickness of 500nm and for various waveguide heights and waveguide widths.

Figure 2.4 shows four calculated mode profiles with fixed waveguide heights and rib etch depths of 0.7  $\mu$ m and 0.5  $\mu$ m, respectively. The waveguide widths varied from 1.0  $\mu$ m to 3.0  $\mu$ m. It can be seen that for the widest waveguide width, the mode lies primarily in the silicon region. As the waveguide width gets narrower, the mode is pushed into the III-V region. Since the III-V region lacks lateral confinement, the mode gets substantially wider. Figure 2.5 shows the calculated confinement factors for the silicon region and the quantum well regions as a function of waveguide width and height. Again, it can be seen that the narrower widths yield higher quantum well confinement factors while the silicon confinement factors are reduced. As the wave guide width becomes wider, the mode moves towards the silicon region and saturates to a value equivalent to the 1-D slab structure. The ability to control the optical mode with the silicon waveguide is a key feature of this platform. Take for

example, if you wanted to integrate amplifiers and lasers with a single chip. Amplifiers are typically designed with low quantum well confinement factors in order to achieve high saturation powers [8], [9], while lasers are designed with higher confinement factors to achieve lower threshold currents. This can still be realized on a single die with a single bond by having narrow waveguide widths in the laser region, while tapering out the waveguide in amplifier regions. The fact that the optical mode is defined by the silicon and can be tailored across the chip, allows major flexibility for photonic integrated circuit design without adding additional complexity to the fabrication process.

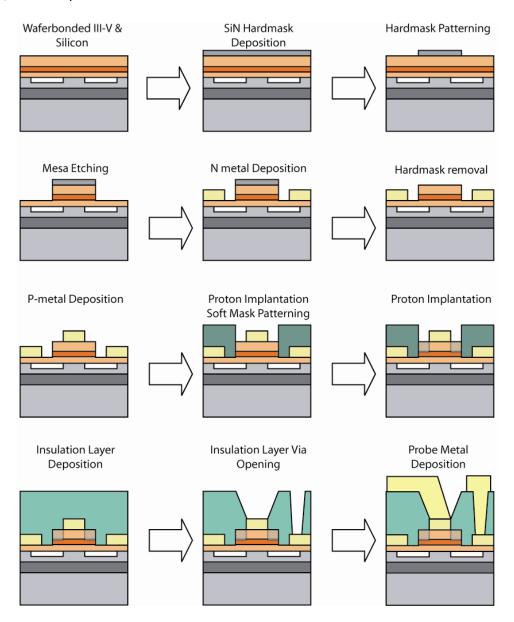

## 2.2 Device Fabrication

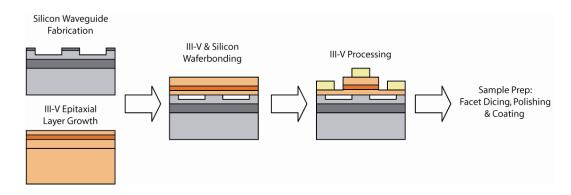

This section will give an overview of processing used to fabricate the various devices reported on in this dissertation. The main flow of the device processing can be divided into 4 major steps as shown in Figure 2.6. First, the pre-bonding process consists of the formation of silicon waveguides on a silicon-on-insulator wafer and the growth of the III-V epitaxial layer structure on the InP substrate. Next, wafer bonding is conducted and the substrate of the InP is removed such that the III-V epitaxial layer structure is transferred to the top surface of the silicon-on-insulator wafer. In the third major step, the post bonding processing is done on the III-V layers in order to manipulate the flow of current in the hybrid regions through the etching of mesas, deposition of contacts, and definition of insulating areas through proton

implants and dielectric layer deposition and patterning. In addition, III-V materials are removed from passive regions. The final step is the sample preparation of the device for testing and characterization. This includes dicing, facet polishing, and the deposition of high reflection or anti reflection coatings, depending on the device being tested. Since this step is unique from device to device, it is not discussed in this section, but will be mentioned in the individual device sections.

Figure 2.6 – Basic silicon evanescent laser process flow.

## 2.2.1 - Silicon Processing

Since a lot of the work reported in this dissertation was in collaboration with Intel Corporation, most of the silicon processing (devices in Chapters 2, 3, and 4) was done in an Intel fabrication facility. This section will briefly describe the process used at UCSB to make silicon rib-waveguides. Although the exact etch conditions used at Intel may vary slightly, the overall process is similar.

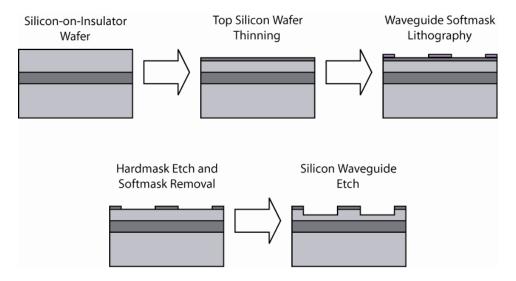

Figure 2.7 – Silicon waveguide fabrication process flow.

Silicon-on-insulator wafers consist of the following structure: a silicon substrate, a thin silicon dioxide layer ( $^{\sim}$  1  $\mu$ m for photonic applications), and a top layer of silicon. Figure 2.7 shows the fabrication process flow. Silicon waveguide processing is done by first thinning the top silicon layer to the desired waveguide height through thermal oxidation. During thermal oxidation, the top silicon is consumed during the formation of an additional silicon dioxide layer at the surface. Next, projection lithography is used to make a soft mask of the waveguides. The soft mask is transferred to the top silicon dioxide layer by inductively coupled plasma etching. The photo-resist is then removed by burning the photo-resist in an  $O_2$  plasma descum chamber followed by a chemical photo resist removal. Finally, the silicon rib waveguides are dry etched by inductively coupled plasma to ensure smooth vertical

sidewalls and hence, low loss waveguides. The silicon is now ready for wafer bonding.

## 2.2.2 Wafer Bonding

Since the lattice spacing of crystalline silicon (5.431 A) and indium phosphide (5.8687 A) has a 7.5% mismatch, wafer bonding is used to transfer the thin InP based active region to the silicon on insulator wafer. Direct wafer bonding is commonly used to mate lattice mismatched semiconductors such as GaAlAs & GaP for high power LEDs, InGaAsP, AlAs & GaAs for improved mirror reflectivity in long wavelength VCSELS, and InGaAsP & AlGaAs for high To lasers [10]. This process consists of the following steps. First a thorough cleaning of the sample surface is done to remove all semiconductor particles that were generated during dicing or cleaving and to remove all organics on the surface, followed by a chemical surface treatment removing any surface oxide states or other stable surface states. The samples are then placed in physical contact with each other and undergo spontaneous bonding and are held together with Van der Waals forces [10]. This bond is relatively strong, depending on the two material systems being bonded, but is further strengthened through a high temperature anneal (typically 600 °C or higher) while applying pressure on the bonded sample. The high temperature anneal results in chemical changes and re-crystallization at the bonded interface, while the pressure on the sample compensates for any waviness or surface roughness and ensures greater surface area contact between the two materials. The substrate of one of the material systems is then removed by using a wet etch resulting in the transfer of one epitaxial layer structure to another.

The thermal expansion coefficient mismatch of silicon ( $\alpha_{si}$  = 2.6 x 10<sup>-6</sup> /K) [11] and InP ( $\alpha_{si}$  = 4.8 x 10<sup>-6</sup> /K) [12] requires the use of a low temperature wafer bonding technique in order to preserve the quality of the transferred epitaxial layers. Equation 2.4 describes the thermal mismatch stress of the bonded wafers as follows [reference]:

(Eq - 2.4)

$$\sigma = \frac{E}{1 - v^2} \left\{ \frac{\frac{E_{InP}}{1 - v_{InP}^2} \alpha_{InP} h_{InP} + \frac{E_{Si}}{1 - v_{Si}^2} \alpha_{Si} h_{Si}}{\frac{E_{InP}}{1 - v_{InP}^2} h_{InP} + \frac{E_{Si}}{1 - v_{Si}^2} h_{Si}} - \alpha \right\} \Delta T$$

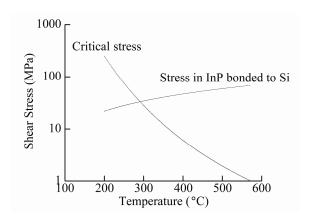

where  $\alpha$  is the thermal expansion coefficient, h is the thickness of the substrate, E is the Young's modulous,  $\nu$  is the Poisson's ratio, and  $\Delta T$  is the difference the bonding temperature and room temperature. This equation is used by Pasquariello *et al.* to express the maximum sheer stress in the <110> direction, the maximum slip system between the alternating indium and phosphide {1,1,1} planes, as a function of temperature as follows [13]:

(Eq - 2.5)

$$\tau_{Sheer} = \frac{2}{\sqrt{6}}\sigma$$

The critical stress required to generate dislocations in InP is empirically formulated by Pasquariello *et al.* using the theory or stress induced dislocation generation [13] is expressed in Equation 2.6.

(Eq - 2.6)

$$\tau_{critical} = 898e^{\frac{5934.17}{T}}$$

Figure 2.8 - Plot of critical dislocation generation stress in InP and sheer stress between InP bonded to silicon versus temperature [Pasquariello *et al.*, reference [13]]

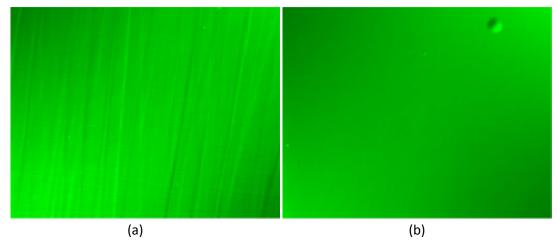

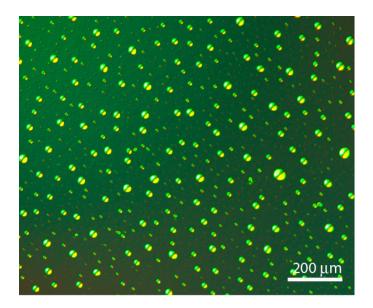

Figure 2.8 shows a plot of the critical stress and the sheer stress as a function of temperature. In order to prevent the generation of dislocations in the InP, the bonding temperature must be kept below 300 °C. Normarski mode microscope images of the surface of III-V epitaxial layers transferred to silicon at (a) 600 °C and (b) 250 °C are shown in Figure 2.9. It can be seen that the sample bonded at higher temperatures shows cross hatching and waviness in the III-V film indicating stress within the film. The low temperature sample, on the other hand, shows a pristine surface, indicating a high III-V film quality. In order to maintain high bond strengths, a low temperature oxygen plasma assisted wafer bonding process, consisting of an O<sub>2</sub> plasma based surface activation prior to the mating of the two surfaces followed by a 250 °C anneal, was pursued. This temperature was raised to 300 °C during device processing in order to further increase bond strength, while not exceeding the 300 °C limit shown in Figure 2.8.

Figure 2.9 Nomarski microscope images, showing the surface roughness of the transferred III-V surface at bonding temperatures of (a) 600 °C and (b) 250 °C.

The low temperature oxygen plasma assisted wafer bonding process begins with the same cleaning processes as the direct bonding approach. This is done by solvent cleaning the silicon and III-V with acetone, isopropanol, and deionized water. Next the samples are placed in a solution of Tergitol:H<sub>2</sub>O (5 drops: 1 liter) and are physically wiped with cleanroom grade q-tips to remove particles. Tergitol is an organic detergent that assists in the removal of surface particles. Next the samples are rinsed in deionized water and inspected under the microscope for particles. The swab and inspect process is repeated until the samples are particle free.

The silicon dioxide hard mask layer used during silicon waveguide fabrication is then removed by using an HF dip. The III-V material is typically grown with a 200 nm InGaAsP cap layer to protect the surface quality during handling and cleaving. This layer is removed with a chemical wet etch and the samples undergo another swab

and inspect step to remove any particles that may have been accumulated during the acid treatments. A final organic clean is done by conducting a 30 minute Ozone clean of the surface.

The samples are then treated with an  $O_2$  Plasma where a thin (<5 nm), highly strained, and highly reactive hydrophilic oxide is formed on the surface. The samples are dipped in deionized water and their surfaces are terminated with OH groups. At this point, the samples are placed in physical contact with each other and spontaneous bonding occurs by the formation of hydrogen bonds. The samples are place in a Suss SB-6, a commercial wafer bonder, at 300 °C with 1.5 MPa of pressure for 12 hours. During this annealing process, the chemistry of the bond changes in a two step process as follows [14]:

$$Si - OH + HO - M \rightarrow Si - O - M + H_2O$$

$2 H_2O + Si \rightarrow SiO_2 + 2H_2$

where M is either indium, or phosphide. The chemical change in the bond, leads to the generation of water. The water then oxidizes the silicon and outgases hydrogen. The outgassed hydrogen at the bonded interface leads to void formations on unpatterned surfaces as shown in Figure 2.10. The rib waveguides in the silicon act as in-plane out-gassing channels, allowing the hydrogen released during the bond to flow out of the sample. Void formation still occurs in regions far from the channels (~150  $\mu$ m) but do not affect device performance since they are away from device regions. The void density can be reduced by conducting the annealing in vacuum and

by increasing the time to 18 hours to allow for hydrogen diffusion out of the bonded interface.

Figure 2.10 – Nomarski microscope images, showing void formation on unpatterned bonded wafers

Although the use of in-plane out-gassing channels is useful to demonstrate devices, it does place constraints on how the waveguides must be layed out on the silicon such that the channel density is high enough to allow for sufficient  $H_2$  removal. A complete study was not done to find the minimum density required to achieve good bonding, but a general design rule was of a maximum spacing of 125  $\mu$ m per channel was used .

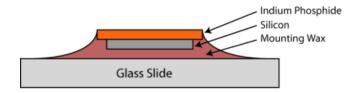

Next, the substrate of the InP is removed in a solution of HCL:H<sub>2</sub>O. This selective etch is designed to stop at the top InGaAs etch stop/p contact layer, protecting the AlGaInAs epitaxial layer structure. To prevent the lateral etching of the epitaxial

layer structure, the sample is mounted onto a glass slide with mounting wax or "crystal bond". The sample is mounted silicon side down. Mounting wax is spread along the four edges of the sample as shown in Figure 2.11.

Figure 2.11: Cross section diagram of bonded sample mounted to a glass slide for sidewall protection during substrate removal.

The sample is reheated to remove it from the glass slide and undergoes a final solvent clean to remove the residual mounting wax and prepare the sample for device processing.

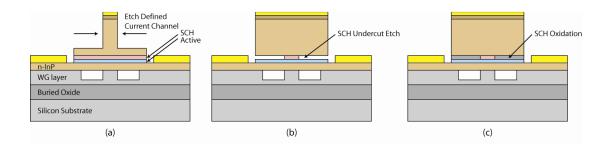

#### 2.2.3 Post-bond Device Process Flow

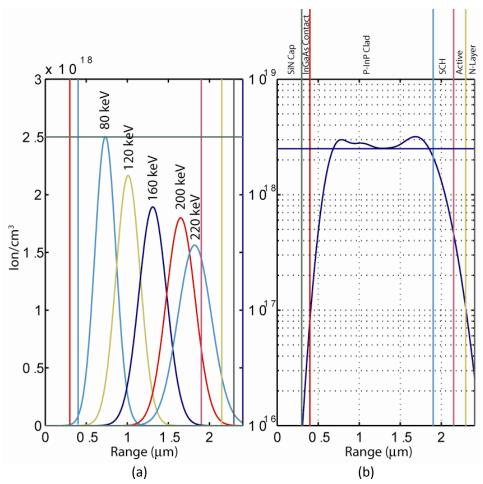

The post-bond device process flow is shown in Figure 2.12. Once the wafers are bonded, mesas need to be etched above the waveguide. This is done by first depositing a thick SiN hard mask on the top III-V surface of the bonded sample. Next the SiN hard mask is patterned with a photo lithographically defined soft mask and is etched with CF<sub>4</sub> in an RIE etch chamber. Next, the photo resist is removed and the P mesas are etched in a two step etch processes. First, a dry etch is done in a reactive ion etch (RIE) chamber using CH<sub>4</sub>/H<sub>2</sub>/Ar. This etch depth is monitored using laser interferometry such that the etch goes through the top InP cladding region, but stops within the SCH/QW region. A wet etch is used to finish the p mesa etch using a solution of H<sub>2</sub>O<sub>2</sub>:H<sub>3</sub>PO<sub>4</sub>:H<sub>2</sub>O. This etch is selective against InP and is designed to etch

through the AlGaInAs materials in the SCH and QW such that the bottom InP layer is exposed. Next, Ni/Ge/Au/Ni/Au N contacts are patterned, deposited, and lifted off via a Bi-layer liftoff process. The SiN hard mask is then removed and Pd/Ti/Pd/Au P contacts are patterned, deposited, and lifted off. The p contact not only serves are a path for current to flow into the mesa, but it also serves as a mask above the waveguide such to prevent the implantation of protons above the waveguide, effectively defining the current path through the mesa. The contacts are then annealed for activation on a strip annealer at 320 °C for 30 seconds and TLM patterns are measured to ensure good contact resistances. Next, a bi-layer structure of PMGI and photo-resist are used to create a mask for proton implant. This mask protects the exposed n regions from implantation maintaining the conductivity of those regions. The samples are then sent out for proton implantation. Upon the return of the samples, the proton implant mask is removed and a dielectric electrical isolation layer is deposited on the surface. Most of the devices fabricated in Chapters 3 and 4 utilize a thick layer of SiN for this insulation layer, while the final device design (Ch. 5) utilizes SU-8 since it is a low k dielectric to lower the device capacitance and it also adds structural integrity to the structure for improved facet polishing. Vias are patterned into this isolation layer and Ti/Au probe pads are patterned and deposited on the sample. The deposition of this layer is done while rotating the sample at an angle as to ensure good sidewall coverage. This completes

the processing and the samples are now ready for device specific sample prep, and/or on-chip device characterization.

Figure 2.12 – III-V post bond process flow.

## 2.3 – Proof of Concept – Optically Pumped Silicon Evanescent Lasers

Optically pumped silicon evanescent lasers were first demonstrated as a proof of concept for the silicon evanescent waveguide architecture. This chapter discusses the device structure and design of the active region, the experimental methods used to test the devices, and discusses the pulsed [1] and continuous wave [2] lasing performance of these devices.

Figure 2.13 – The optical pumped silicon evanescent laser device structure cross section

#### 2.3.1 - Device Structure

Figure 2.13 shows a cross sectional diagram of the optically pumped device. The device is the simplest of all SELs and consists only of a III-V active region structure designed for optical pumping bonded to silicon rib waveguides.

The III-V active layer structure is shown in Table 2.1. The structure is designed to be optically pumped from the top surface through the InP cladding in the 900 nm to 1275 nm wavelength range, with the pump light being absorbed in the SCH region. The pump light field intensity decays as it is absorbed, generating a carrier profile in the SCH. This carrier distribution causes the carriers to flow from the SCH into the quantum wells where they recombine, generating spontaneous emission and optical gain at 1550 nm. A thin super lattice region is used in this structure between the lower SCH InP region and the InP bonding layer to prevent the propagation of defects from the bonded interface to the quantum wells [15].

| III-V Epitaxial growth layer structure |                                                                                                                                                            |           |  |  |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--|--|

| Name                                   | Composition                                                                                                                                                | Thickness |  |  |

| Etch stop layer                        | $In_{0.53}Ga_{0.47}As$                                                                                                                                     | 0.1 μm    |  |  |

| Cladding                               | InP                                                                                                                                                        | 1.5 μm    |  |  |

| Upper SCH                              | Al <sub>0.131</sub> Ga <sub>0.34</sub> In <sub>0.528</sub> As, 1.3 μm                                                                                      | 0.5 μm    |  |  |

| Quantum Wells                          | _Al <sub>0.089</sub> Ga <sub>0.461</sub> In <sub>0.45</sub> As, 1.3 μm (6x)<br>Al <sub>0.055</sub> Ga <sub>0.292</sub> In <sub>0.653</sub> As, 1.7 μm (5x) | 10 nm     |  |  |

| Quartarii Wens                         | $L_{\text{Al}_{0.055}}$ Ga <sub>0.292</sub> In <sub>0.653</sub> As, 1.7 µm (5x)                                                                            | 7 nm      |  |  |

| Lower SCH                              | Al <sub>0.131</sub> Ga <sub>0.34</sub> In <sub>0.528</sub> As, 1.3 μm                                                                                      | 0.05 μm   |  |  |

| Lower SCH barrier                      | InP                                                                                                                                                        | 110 nm    |  |  |

| Super Lattice                          | $\Gamma_{0.85}^{\text{In}_{0.85}\text{Ga}_{0.15}\text{As}_{0.327}\text{P}_{0.673}(2x)}$                                                                    | 7.5 nm    |  |  |

| Super Luttice                          | └InP (2x)                                                                                                                                                  | 7.5 nm    |  |  |

| Bonding layer                          | InP                                                                                                                                                        | 10 nm     |  |  |

|                                        |                                                                                                                                                            |           |  |  |

Table 2.1 – Optically pumped III-V layer structure

#### 2.3.2 Experimental set up and method

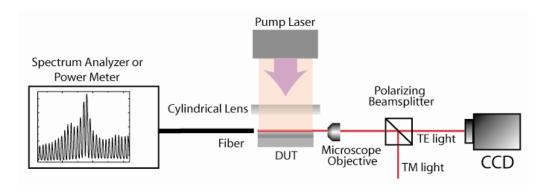

Figure 2.14 shows the experimental set up. The devices are pumped perpendicular to the top surface. The pump beam cross section should ideally be rectangular such that the entire device length of 600-900  $\mu m$  is pumped, and the width of the beam is

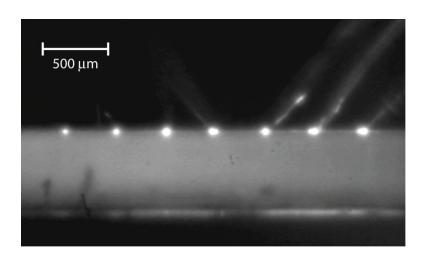

as closely matched to the device width as possible (~ 1 - 4  $\mu$ m). A fiber coupled 980 nm laser diode and a 2 W 1250 nm fiber laser were used as optical pumps for pulsed and continuous wave operation, respectively. The pump light is first collimated and focused onto the top surface of the laser through a cylindrical lens forming a 0.916 mm by 12  $\mu$ m ellipse. The pump system was positioned with an XYZ stage. This system was place on a sliding rail along with a top surface imaging system such that they could be interchanged easily.

Figure 2.14 – The experimental setup for testing optically pumped silicon evanescent lasers

The light from the device is collected at one facet with a lensed fiber and routed to a spectrum analyzer or a power meter, depending on the measurement being made. The other facet is imaged with an infrared imaging system. The system consists of an 80X microscope objective, with a modified Navitar telescoping zoom system mounted on a Hamamatsu infrared camera. The Navitar zoom system's front lens was removed such that higher magnifications could be achieved with the 80X microscope objective. In addition, a polarizing beam splitter can be placed in the

optical path such that TE or TM polarization images can be observed independently. This imaging system has proved to be quite useful for testing these devices since it allows us to assess the waveguide facet quality, ensure we have proper alignment during other experiments in which we launch light from the fiber into the waveguide, and give us an experimental way to verify which mode lases and if the waveguide is single mode.

#### 2.3.3 - Pulsed Operation

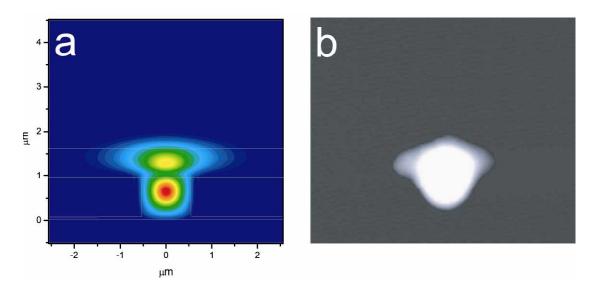

The 980 nm optical pump was driven at 1 microsecond pulse width and 4% duty cycle. This allowed us to operate the optical pump with peak powers of ~ 1W, far above the 300 mW maximum continuous wave operating power. Figure 2.15 shows the computed optical mode and the near-field image of lasing optical mode, showing good qualitative agreement. The lasing mode was TE with a TE/TM ratio of > 20 dB.

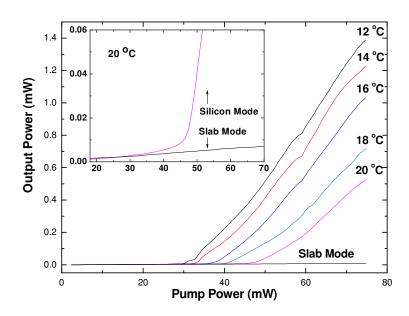

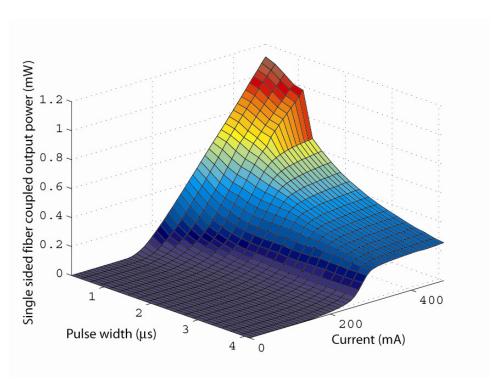

Figure 2.16 shows the peak single sided fiber coupled output power of the laser as a function peak pump power (Light vs. Light curve). The lasers lased up to 20 °C with a maximum fiber coupled power of 1.4 mW and a minimum threshold 30 mW. The single output differential quantum efficiency is approximately 3.2 % at 12 °C, the total efficiency taking into account the light from both facets and the estimated 5 dB coupling loss is approximately 20 %. It is important to note that lasing only occurs in the optical mode defined by the Si waveguide region. In other words, slab modes in

the III-V region do not support lasing. This can be seen from the inset of Figure 2.15, which compares the light output for pumping in the two regions.

Figure 2.15 - a) The simulated optical mode superimposed over the waveguide structure. b) The nearfield image of the lasing optical mode.

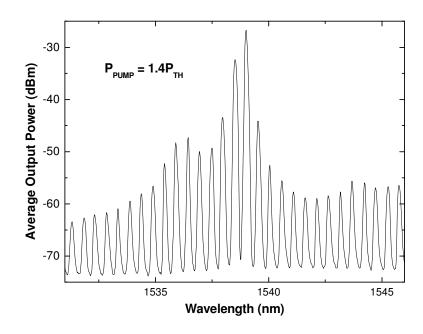

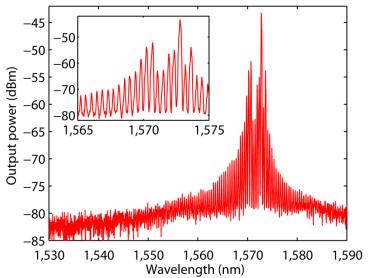

Figure 2.17 shows the lasing spectrum at 1.4 times the threshold pump power and at a temperature of 12 °C. The optical spectrum consists of the expected Fabry-Pérot response for the 600  $\mu$ m long cavity, with a group index of 3.7. The devices were limited to pulsed lasing due to the maximum power available.

Figure 2.16 – Pulsed L-L curves as a function of temperature. (inset) L-L curve of device when pumped above the silicon waveguide and above the silicon slab without lateral modal confinement

Figure 2.17 – Optically pumped pulsed lasing spectrum

#### 2.3.4 - Continuous wave operation

Continuous wave operation was achieved by replacing the 980 nm laser diode with a 2 W fiber laser operating at 1250 nm. A second batch of devices was fabricated with a variety of waveguide widths such that their modal characteristics could be observed.

The lasing optical modes as a function of waveguide width with their corresponding simulated optical modes is shown in Figure 2.18. As you can see, for narrow silicon waveguide widths, the mode lies primarily in the III-V region and as the widths become wider and wider, the optical mode lies more and more in the silicon region, as predicted by simulations.

Figure 2.18 – Experimentally captured near field profiles of the lasing modes and their corresponding calculated mode profiles for various waveguide widths.

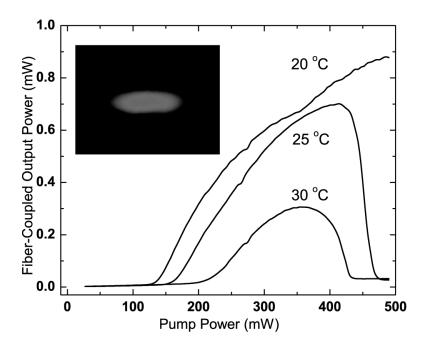

The lasers operated in continuous wave mode, with widths less than 1.5  $\mu$ m operating with a single transverse mode, while wider widths lased with multiple transverse modes. Figure 2.19 shows the L-L curve of 1  $\mu$ m waveguide width laser operating up to 30 °C. It can be seen that the L-L curve is relatively clean with very minimal kinks in its shape. The optical mode was observed throughout the various

operating conditions and showed stable lasing in the fundamental mode. The maximum fiber coupled laser output power was 0.9 mW. The total maximum output power including the output from both facets and coupling losses is approximately of 5 mW with a slope efficiency of 2.8%.

Figure 2.19 - L-L curve for a waveguide width of 1  $\mu m$  and the corresponding optical mode.

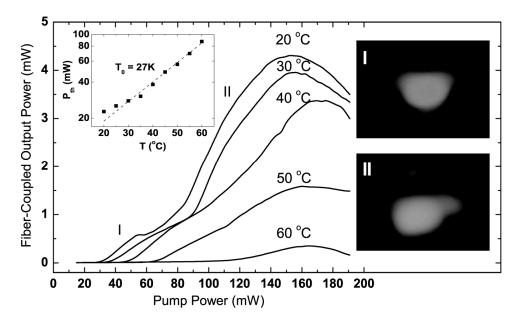

In Figure 2.20, a 4  $\mu$ m wide device is operating with a threshold pump power of 23 mW with a fiber-coupled maximum output power of 4.5 mW and a slope efficiency of 3% at 20 °C. The total maximum output power taking into account the light from both facets and the coupling losses of 5 dB is approximately 28 mW and the corresponding slope efficiency is 16%. The threshold increases from 23 to 105 mW between 20 °C and 60 °C and the structure exhibits a temperature coefficient of 27

K. The kinks in the LL curves are due to the multimode lasing with wide waveguide dimension. It is clearly shown from two different mode profiles in Figure 2.20 that higher modes are superimposed with a fundamental mode at the region II of the LL curve while only a fundamental mode is lasing at the region I.

Figure 2.20 - L-L curve for a waveguide width of 4  $\mu$ m and the corresponding optical mode at two pump powers. Inset: Threshold as a function of temperature.

### 2.5 – *Summary*

The silicon evanescent waveguide structure is presented in this chapter. The device consists of a III-V gain structure bonded to a silicon on insulator rib waveguide to allow for evanescent coupling of the silicon waveguide mode into the III-V region to achieve gain. The design of optical mode characteristics is presented showing the ability to tailor the modal profile based on silicon waveguide definition. The fabrication of these devices is discussed. In particular, the transfer of the III-V active

layer from an InP substrate to a silicon wafer through a low temperature wafer bonding process is presented. Optically pumped lasers are demonstrated as a proof of concept for the device architecture. The lasers show continuous wave lasing up to 60 °C with a maximum fiber coupled output power of 4.5 mW at 20 °C. The lasers modal characteristics are shown to be strongly dependent on the silicon waveguide formation by comparing the lasing performance of regions with and without lateral confinement in the silicon, with the later showing no lasing. In addition, the experimental observation of the optical mode verifies that the optical mode can be manipulated across a single silicon chip by changing the waveguide width.

#### References

- [1] H. Park, A. W. Fang, S. Kodama, and J. E. Bowers, "Hybrid silicon evanescent laser fabricated with a silicon waveguide and III-V offset quantum wells,"

Optics Express, 13, 9460-9464, (2005)

- [2] W. Fang, H. Park, R. Jones, O. Cohen, M. J. Paniccia, J. E. Bowers, "A Continuous-Wave Hybrid AlGaInAs—Silicon Evanescent Laser," IEEE Photonics Technology Letters, Vol. 18, Issue 10, pg 1143 1145 (2006)

- [3] L. A. Coldren and S. W. Corzine, *Diode Lasers and Photonic Integrated Circuits*, New York: John Wiley & Sons, Inc., pp. 432 (1995)

- [4] L. A. Coldren and S. W. Corzine, *Diode Lasers and Photonic Integrated Circuits*, New York: John Wiley & Sons, Inc., pp. 39 (1995)

- [5] L. A. Coldren and S. W. Corzine, *Diode Lasers and Photonic Integrated Circuits*, New York: John Wiley & Sons, Inc., pp. 45 (1995)

- [6] Yariv, and P. Yeh. *Photonics,* New York, Oxford University Press, pp. 196 (2007)

- [7] B.E.A. Saleh and M.C. Teich, *Fundamentals of Photonics,* New York: John Wiley & Sons, Inc., pp. 248 (1991)

- [8] K. Morito, S. Tanaka, S. Tomabechi, and A. Kuramata, "A broadband MQW semiconductor optical amplifier with high saturation output power and low noise figure". Semiconductor Optical Amplifiers and their Applications Meeting, PD1-1, San Francisco, CA June 30 2004.

- [9] P. W. Juodawlkis, J. J. Plant, R. K. Huang, L. J Missaggia, and J. P. "High Power 1.5μm InGaAsP-InP Slab-Coupled Optical Waveguide Amplifier," IEEE Photon. Technol. Letts. vol. 17, Feb, 2005.

- [10] Black, A. R. Hawkins, N. M. Margalit, D. I. Babic, A. L. Holmes, Jr., Y.-L. Chang, P. Abraham, J. E. Bowers and E. L. Hu, "Wafer Fusion: Materials Issues and Device Results," IEEE Journal of Selected Topics in Quantum Electronics, 3(3), 943-951, (1997)

- [11] The Thermal Properties of Silicon. Retrieved 25 January, 2008, http://www.ioffe.rssi.ru/SVA/NSM/Semicond/Si/thermal.html

- [12] The Thermal Properties of Indium Phosphide (InP). Retrieved 25 January, 2008, http://www.ioffe.rssi.ru/SVA/NSM/Semicond/InP/thermal.html

- [13] D. Pasquariello, M. Camacho, F. Ericsson, and K. Hjort, "Crystalline Defects in InP-to-Silicon Direct Wafer Bonding," Jpn. J. Appl. Phys. Vol. 40, pp. 4837-4844, (2001)

- [14] U. Gosele, and Q.-Y. Tong, "Semiconductor wafer bonding," Annual Review of Materials Science, 1998, Vol. 28 Issue 1, p21

- [15] Karim, K. A. Black, P. Abraham, D. Lofgreen, Y. J. Chiu, J. Piprek, and J. E. Bowers, "Super lattice barrier 1528-nm vertical-cavity laser with 85°C continuous-wave operation," IEEE Photon. Technol. Lett. 12, 1438-1440 (2000).

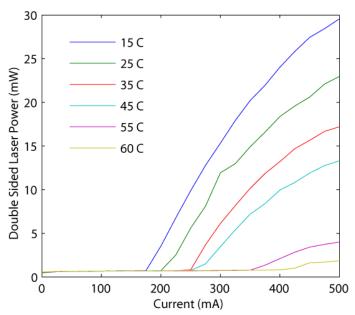

# Chapter 3 - Electrically Pumped Silicon Evanescent Lasers - Fabry - Perot Lasers

This chapter reports on the first electrically pumped silicon evanescent laser [1]. All results reported in this chapter utilize a Fabry-Perot laser topography. The first section of this chapter describes pulsed lasing operation with a simplified device structure used to validate the epitaxial layer design for current injection without lateral current confinement structures. The second section of the chapter presents the design of a lateral current confinement structure through the use of proton implantation and discusses continuous lasing operation. Lastly, this chapter presents a second generation electrically pumped laser structure for improved lasing performance and compares the thermal performance of the two generations.

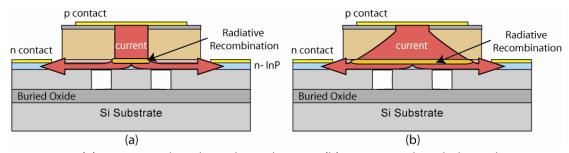

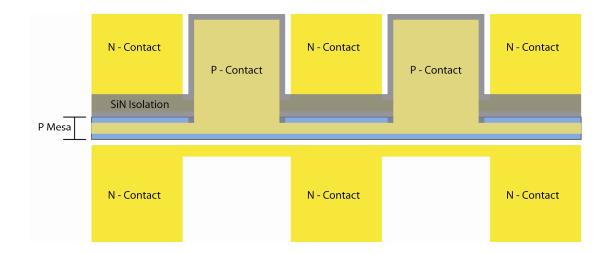

## 3.1 - Pulsed Lasing Device Structure

The device diagram for the first generation electrically pumped silicon evanescent lasers is shown in Figure 3.1. The III-V mesa regions were 75  $\mu$ m wide such that the p-contact could be easily probed from the top. N-contacts were placed 5  $\mu$ m away both sides of the mesa. In order to keep the device structure simple, no lateral current confinement was used in the p region. Instead, a 6  $\mu$ m wide current aperture was used at the center of a 300 nm thick silicon nitride isolation layer

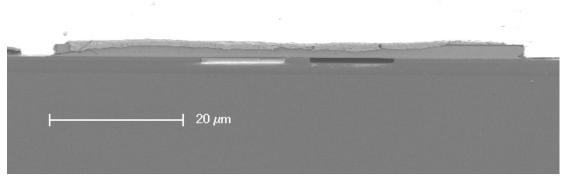

under the p-contact. A scanning electron microscope image of the device is shown in Figure 3.2.

Figure 3.1 – The device cross section for the electrically pumped silicon evanescent pulsed laser.

Figure 3.2 – Scanning electron microscope image of the electrically pumped silicon evanescent pulsed laser device cross section.

The buried oxide, silicon waveguide width, and height were 2  $\mu$ m, 2  $\mu$ m, and 0.76  $\mu$ m based on the criteria described in chapter 2. The rib was unintentionally etched all the way to the buried oxide, resulting in a strip waveguide. However, the confinement factors were not significantly perturbed in the deeply etch regime. The resulting silicon waveguide and quantum well confinement factors calculated using

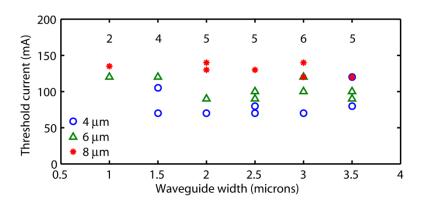

Rsoft Beamprop were 74% and 5.5%, respectively. The laser's facets were diced and polished resulting in a total cavity length of ~780  $\mu$ m. Other waveguide widths of 1  $\mu$ m, 1.5  $\mu$ m, 2.5  $\mu$ m, 3  $\mu$ m, and 3.5  $\mu$ m were also fabricated and tested, but are not presented in detail here since the 2  $\mu$ m width devices showed the best overall performance. The variation of device performance due to facet polishing created scatter in the laser thresholds and differential efficiencies such that relationships between width and device performance could not be established.

III-V Epitaxial growth layer structure

| Name                 | Composition                                                                                       | Doping Concentration                  | Thickness |

|----------------------|---------------------------------------------------------------------------------------------------|---------------------------------------|-----------|

| P contact layer      | P-type In <sub>0.53</sub> Ga <sub>0.47</sub> As                                                   | 1 x 10 <sup>19</sup> cm <sup>-3</sup> | 0.1 μm    |

| Cladding             | P-type InP                                                                                        | 1 x 10 <sup>18</sup> cm <sup>-3</sup> | 1.5 μm    |

| Separate Confinement |                                                                                                   |                                       |           |

| Heterostructure      | P-type Al <sub>0.131</sub> Ga <sub>0.34</sub> In <sub>0.528</sub> As, 1.3 μm                      | 1 x 10 <sup>17</sup> cm <sup>-3</sup> | 0.25 μm   |

| Quantum Wells        | ΓAl <sub>0.089</sub> Ga <sub>0.461</sub> In <sub>0.45</sub> As, 1.3 μm (9x)                       | undoped                               | 10 nm     |

|                      | $L_{Al_{0.055}}Ga_{0.292}In_{0.653}As, 1.7 \mu m (8x)$                                            | undoped                               | 7 nm      |

| N layer              | N-type InP                                                                                        | 1 x 10 <sup>18</sup> cm <sup>-3</sup> | 110 nm    |

| Super Lattice        | $\Gamma$ N-type In <sub>0.85</sub> Ga <sub>0.15</sub> As <sub>0.327</sub> P <sub>0.673</sub> (2x) | 1 x 10 <sup>18</sup> cm <sup>-3</sup> | 7.5 nm    |

| super Eutrice        | N-type InP (2x)                                                                                   | 1 x 10 <sup>18</sup> cm <sup>-3</sup> | 7.5 nm    |

| N bonding layer      | N-type InP                                                                                        | 1 x 10 <sup>18</sup> cm <sup>-3</sup> | 10 nm     |

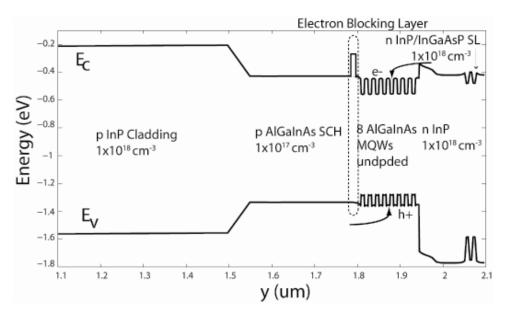

Table 3.1 – Electrically pumped III-V epitaxial layer structure transferred to silicon.

The epitaxial layer structure used in the electrically pumped devices is shown in Table 3.1. It is similar to the optically pumped devices except for a few modifications. First, N layers (S dopant) and P layers (Zn dopant) were added to the structure such that current could be injected into the quantum well region. The region below the quantum wells (closer to the silicon waveguide after bonding) was doped N type since N type InP has lower optical loss and electrical resistance than P type for a given doping level [2]. This is important because this layer goes through the optical mode, and needs to be as low loss as possible to minimize threshold

currents. Additionally, this layer needs to be low resistance in order to minimize carrier spreading in the active region. The second change, was the removal of the lower SCH layer such that the quantum wells would be closer to the silicon waveguide, thereby increasing the active region confinement factor.

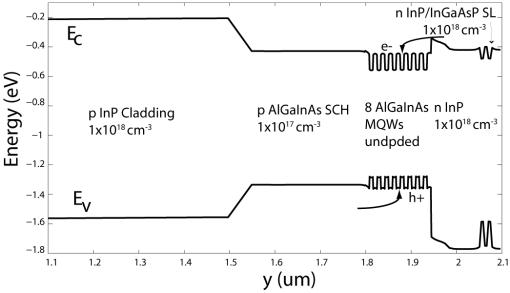

Figure 3.3 – The band diagram of the doped SEL epitaxial layer structure.

Figure 3.3 shows the band structure of the doped epitaxial structure with the P-InP cladding to the left, and the N-layers to the right. Holes are injected to the right from the p-region where they flow through the SCH layers into the quantum well. Electrons are injected from the N-InP layer on the right where they flow left into the quantum wells. At higher temperatures, it is possible that the electrons would have enough energy to escape the wells and flow into the SCH region, reducing the injection efficiency.

## 3.2 – Pulsed Lasing Operation

The laser is driven by applying a  $0.5~\mu s$  long square-wave current pulse with a 4~% duty cycle to the top p and n-contacts. The laser output from one facet is collected by a lensed single mode fiber and detected by a spectrum analyzer or photodetector.

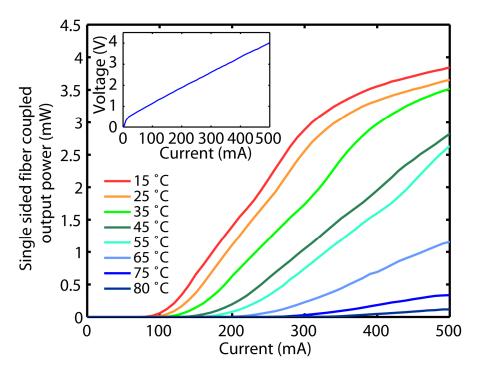

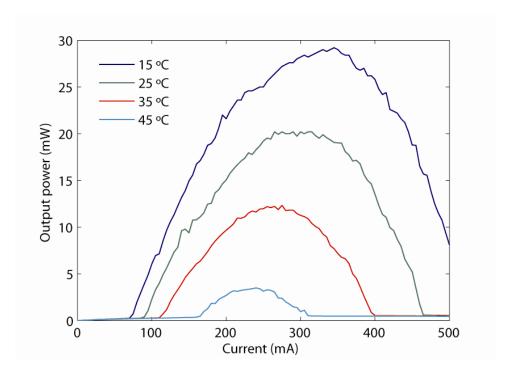

Figure 3.4 - The single sided fiber coupled laser output as a function of drive current for various temperatures. The inset displays the voltage - current characteristics of the laser.

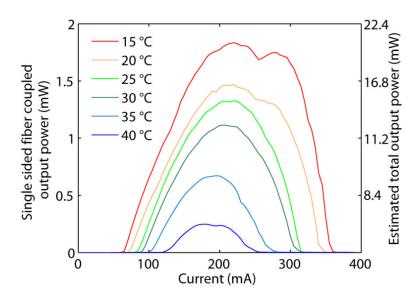

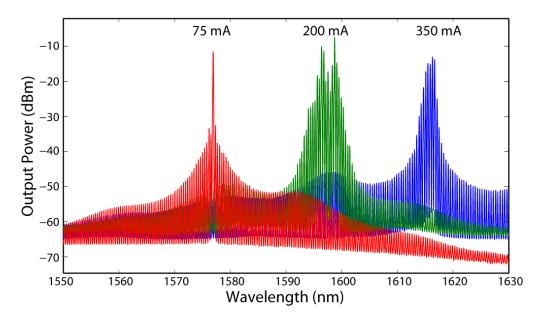

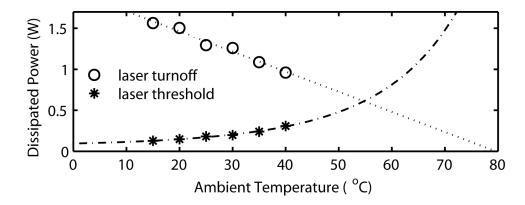

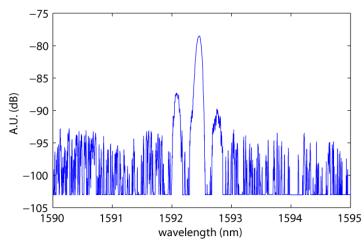

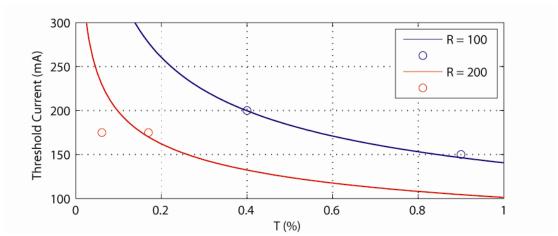

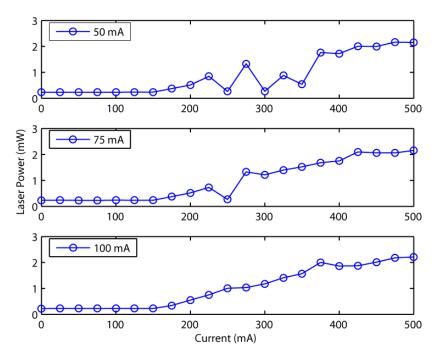

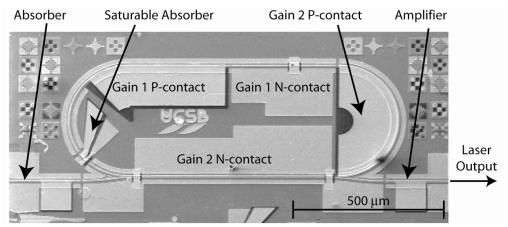

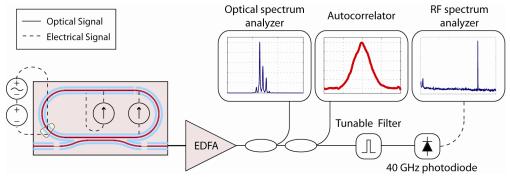

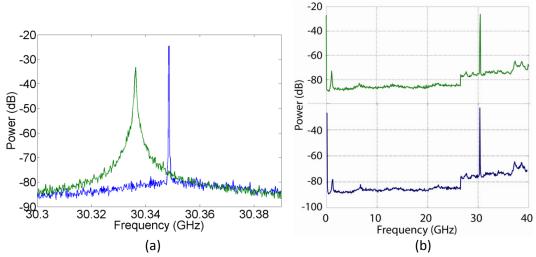

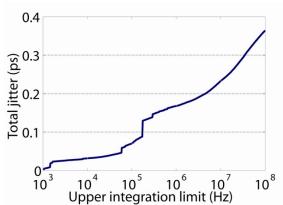

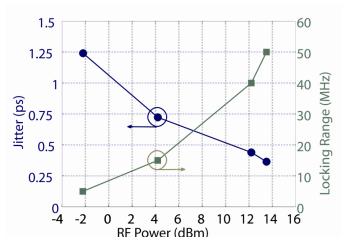

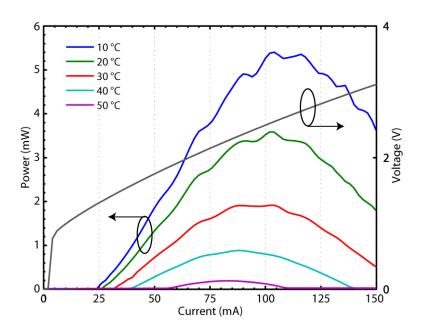

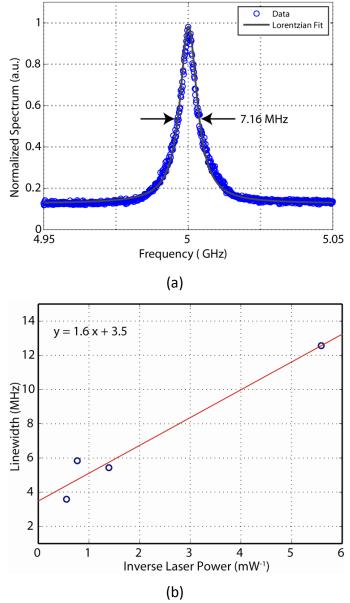

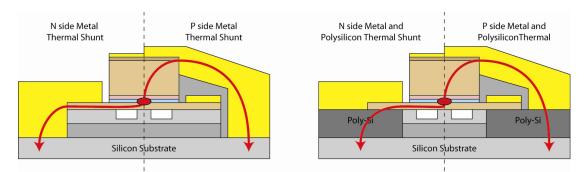

Figure 3.4 shows the measured laser output power as a function of injected current for various temperatures ranging from 15 to 80 °C. As can be seen from the figure, the laser threshold is 120 mA with a maximum power of 3.8 mW at 15 °C. Using the